Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Контроль по четности

|

|

Пусть имеется цепочка информационных бит длиной k0. Добавим к ним контрольный бит kс, значение которого определяется тем, что новая кодовая цепочка из k0+1 бита должна содержать четное количество единиц – по этой причине такой контрольный бит называется битом четности.

Например,

- для информационного кода 01010100 бит четности будет иметь значение 1,

- для кода 11011011 бит четности равен 0.

В случае одиночной ошибки передачи число 1 перестает быть четным, что и служит свидетельством сбоя.

Например, в случае получения сообщения 101101111 становится понятным, что передача произведена с ошибкой, поскольку общее количество единиц равно 7, т.е. нечетно.

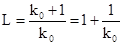

В каком бите содержится ошибка при таком способе кодирования установить нельзя. Избыточность кода в данном случае, очевидно, равна:  =1+1/8=1, 125.

=1+1/8=1, 125.

На первый взгляд кажется, что путем увеличения k0 можно сколь угодно приближать избыточность к ее минимальному значению (Lmin = 1).

Однако с ростом k0:

- растет вероятность парной ошибки, которая контрольным битом не отслеживается;

- при обнаружении ошибки потребуется заново передавать много информации.

Поэтому обычно k0 = 8 или 16 и, следовательно, L=1, 125 (1, 0625).

В наше время использование битов четности является типовым решением для контроля сохранности данных в основной памяти. Хотя внешне создается впечатление, что ПК используют восьмиразрядные ячейки памяти, в действительности они являются девятиразрядными, причем девятый бит используется как контрольный. Каждый раз, когда в память записывается некоторая восьмибитовая комбинация, схема управления памятью автоматически добавляет к ней требуемый контрольный бит. При считывании информации схема управления памятью подсчитывает количество единиц в полученной комбинации. Если ошибка не обнаружиться, контрольный бит удаляется, в противном случае схема управления памяти возвращает считанное восьмиразрядное значение с указанием, что оно искажено и может отличаться от исходного.

— Регулярная проверка качества ссылок по более чем 100 показателям и ежедневный пересчет показателей качества проекта.

— Все известные форматы ссылок: арендные ссылки, вечные ссылки, публикации (упоминания, мнения, отзывы, статьи, пресс-релизы).

— SeoHammer покажет, где рост или падение, а также запросы, на которые нужно обратить внимание.

SeoHammer еще предоставляет технологию Буст, она ускоряет продвижение в десятки раз, а первые результаты появляются уже в течение первых 7 дней. Зарегистрироваться и Начать продвижение

|

|