Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Моделирование исследуемых схем на ЭВМ с применением пакета Multisim

|

|

В данной лабораторной работе комбинационные схемы на сумматорах исследуются моделированием их на ЭВМ с помощью пакета прикладных программ Electronics Workbench версии 6.2 (Multisim), а также в пакете Max+ Plus2.

При выполнении лабораторной работы используются полусумматоры, сумматоры и разрядные сумматоры.

Блок создаётся нажатием клавиш «CTRL» + «B».

Таблица 6.6 Таблица истинности полусумматора

| A | B | P | S |

Таблица 6.7 Таблица истинности одноразрядного сумматора

| A | B | P0 | S | P |

Таблицу истинности для микросхем можно получить сначала выделив её, а затем нажав клавишу F1.

Вам необходимо собрать схему согласно Вашему варианту. Провести моделирование. Получите таблицы истинности для схемы. Сумматоры берутся из библиотек, описанных в первой работе.

6.6 Порядок проведения работы в пакете MAX+plus II

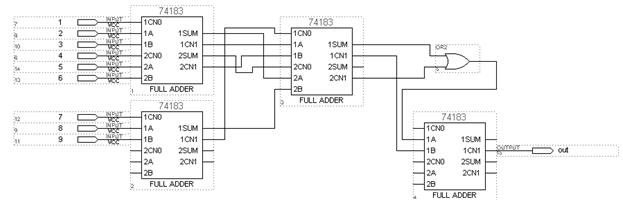

В качестве примера приведем построение пороговой схемы 5/9. На входе будет единица, если на 5-ти или более входов будет единица.

Сумматоры в пакете MAX+plus II сдвоенные, т.е. два полных сумматора объединены в одной схеме. Это позволяет упростить построение.

Схема имеет номер 74183 (FULL ADDER) и находится в библиотеке mf.

В соответствии с порядком создания пороговой схемы, приведенном выше, получаем:

Рис. 6.61 Пороговая схема 5/9

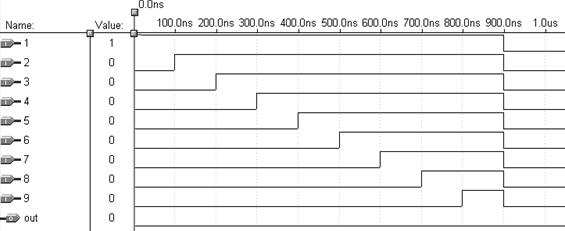

Задаем входные сигналы. Для этого подаем последовательно единицу сначала на один вход, затем на два и т.д.:

Рис. 6.62 Входные сигналы

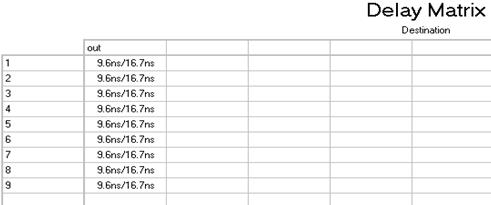

Запускаем компилятор, затем симулятор. Проводим анализ временных задержек между входами и выходом:

Рис. 6.63 Матрица задержек

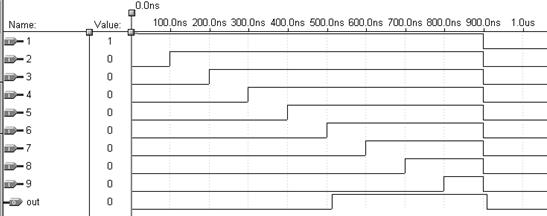

Нажав в окне симулятора кнопку Open SCF, получаем результат работы схемы:

Рис. 6.64 Временные диаграммы

Из графика видно, схема срабатывает тогда, когда больше, чем на четырех входах сигнал высокого уровня (единица), что и требуется по заданию.

Контрольные вопросы

— Регулярная проверка качества ссылок по более чем 100 показателям и ежедневный пересчет показателей качества проекта.

— Все известные форматы ссылок: арендные ссылки, вечные ссылки, публикации (упоминания, мнения, отзывы, статьи, пресс-релизы).

— SeoHammer покажет, где рост или падение, а также запросы, на которые нужно обратить внимание.

SeoHammer еще предоставляет технологию Буст, она ускоряет продвижение в десятки раз, а первые результаты появляются уже в течение первых 7 дней. Зарегистрироваться и Начать продвижение

1. Чем отличается полусумматор от сумматора? Как построить сумматор для n-разрядных чисел?

2. По каким признакам классифицируют сумматоры?

3. Что называется пороговой схемой и для решения каких задач она применяется?

4. Что называется мажоритарным элементом и для решения каких задач он применяется?

5. Как формируется код Грея и для решений каких задач он используется?

6. Что такое умножители двоичных чисел?

7. Для чего применяются умножители?

8. Какие умножители называются матричными?

9. Какие виды умножителей Вы еще знаете?

10. В чем отличие матричного умножителя от быстрого умножителя?

11. В чем отличие матричного умножителя от последовательного умножителя?

12. В чем отличие последовательного умножителя от быстрого умножителя?

13. Что такое частичные произведения?

14. Какой метод вычисления произведения называется модифицированным алгоритмом Бута?

15. Почему все вычисления проще выполнять при представлении чисел в двоичном коде?

16. Какой метод умножения называется последовательным?

|

|