Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

⚡️ Для новых пользователей первый месяц бесплатно. А далее 290 руб/мес, это в 3 раза дешевле аналогов. За эту цену доступен весь функционал: напоминание о визитах, чаевые, предоплаты, общение с клиентами, переносы записей и так далее.

✅ Уйма гибких настроек, которые помогут вам зарабатывать больше и забыть про чувство «что-то мне нужно было сделать».

Сомневаетесь? нажмите на текст, запустите чат-бота и убедитесь во всем сами!

Структура процессорного элемента

|

|

В большинстве матричных SIMD-систем в качестве процессорных эле-ментов применяются простые RISC-процессоры с локальной памятью ограниченной емкости. Например, каждый ПЭ системы MasPar MP-1 состоит из четырехразрядного процессора с памятью емкостью 64 Кбайт. В системе MPP используются одноразрядные процессоры с памятью 1 Кбит каждый, а в СМ-2 процессорный элемент представляет собой одноразрядный процессор с 64 Кбит локальной памяти. Благодаря простоте ПЭ массив может быть реализован в виде одной сверхбольшой интегральной микросхемы (СБИС). Это позволяет сократить число связей между микросхемами и габариты ВС. Одна СБИС в системе СМ-2 содержит 16 процессоров (без блоков памяти), а в системе MasPar MP-1 СБИС состоит из 32 процессоров (также без блоков памяти).

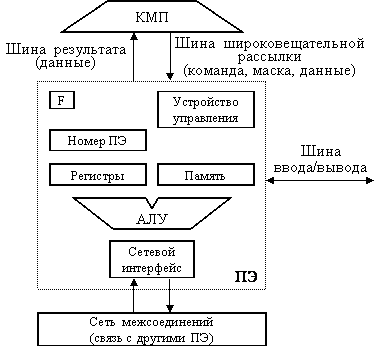

Неотъемлемыми компонентами ПЭ (рис. 8.4) в большинстве вычислительных систем являются:

§ арифметико-логическое устройство (АЛУ);

§ регистры данных;

§ сетевой интерфейс (СИ), который может включать в свой состав регистры пересылки данных;

§ номер процессора;

§ регистр флага разрешения маскирования (F);

§ локальная память.

Рис. 8.4. Модель процессорного элемента

Процессорные элементы, управляемые командами, поступающими по широковещательной шине из КМП, могут выбирать данные из своей локальной памяти и регистров, обрабатывать их в АЛУ и сохранять результаты в регистрах и локальной памяти. ПЭ могут также обрабатывать те данные, которые поступают по шине широковещательной рассылки из КМП. Кроме того, каждый процессорный элемент вправе получать данные из других ПЭ и отправлять их в другие ПЭ по сети соединений, используя для этого свой сетевой интерфейс. В некоторых матричных системах (например в MasPar MP-1) элемент данных из ПЭ-источника можно непосредственно передавать в ПЭ-прием-ник, в то время как в других (например в МРР) данные предварительно должны быть помещены в специальный регистр пересылки данных, входящий в состав сетевого интерфейса. Пересылка данных между ПЭ и устройствами ввода/вывода осуществляется через шину ввода/вывода ВС. В ряде систем (MasPar MP-1) ПЭ подключены к шине ввода/вывода посредством сети соединений и канала ввода/вывода системы. Результаты вычислений любой ПЭ выдает в КМП через шину результата.

Каждому из N ПЭ в массиве процессоров присваивается уникальный номер, называемый также адресом ПЭ, который представляет собой целое число от 0 до N –1. Чтобы указать, должен ли данный ПЭ участвовать в общей операции, в его составе имеется регистр флага разрешения F. Состояние этого регистра определяют сигналы управления из КМП, либо результаты операций в самом ПЭ, либо и те и другие совместно.

Еще одной существенной характеристикой матричной системы является способ синхронизации работы ПЭ. Так как все ПЭ получают и выполняют команды одновременно, их работа жестко синхронизируется. Это особенно важно в операциях пересылки информации между ПЭ. В системах, где обмен производится с четырьмя соседними ПЭ, передача информации осуществляется в режиме «регистр-регистр».

|

|