Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

⚡️ Для новых пользователей первый месяц бесплатно. А далее 290 руб/мес, это в 3 раза дешевле аналогов. За эту цену доступен весь функционал: напоминание о визитах, чаевые, предоплаты, общение с клиентами, переносы записей и так далее.

✅ Уйма гибких настроек, которые помогут вам зарабатывать больше и забыть про чувство «что-то мне нужно было сделать».

Сомневаетесь? нажмите на текст, запустите чат-бота и убедитесь во всем сами!

Структура матричной вычислительной системы

|

|

План лекции.

1. Понятие матричной вычислительной системы и ее отличие от векторной вычислительной системы.

2. Структура матричной вычислительной системы.

3. Интерфейсная вычислительная машина.

4. Массив процессоров и его контроллер.

5. Структура процессорного элемента.

6. Подключение и отключение процессорных элементов.

7. Сети взаимосвязей процессорных элементов.

Понятие матричной вычислительной системы и ее отличие от векторной вычислительной системы

Назначение матричных вычислительных систем во многом схоже с назначением векторных ВС – обработка больших массивов данных. В основе матричных систем лежит матричный процессор (array processor), состоящий из регулярного массива процессорных элементов (ПЭ). Системы подобного типа имеют общее управляющее устройство, генерирующее поток команд, и большое число ПЭ, работающих параллельно и обрабатывающих каждый свой поток данных. С целью обеспечения достаточной эффективности системы при решении широкого круга задач необходимо организовать связи между процессорными элементами так, чтобы наиболее полно загрузить процессоры работой. Именно характер связей между ПЭ и определяет разные свойства системы.

Между матричными и векторными системами есть существенная разница. Матричный процессор интегрирует множество идентичных функциональных блоков (ФБ), логически объединенных в матрицу и работающих в SIMD-стиле. Не столь существенно, как конструктивно реализована матрица процессорных элементов – на едином кристалле или на нескольких. Важен сам принцип – ФБ логически скомпонованы в матрицу и работают синхронно, т.е. присутствует только один поток команд для всех. Векторный процессор имеет встроенные команды для обработки векторов данных, что позволяет эффективно загрузить конвейер из функциональных блоков. В свою очередь, векторные процессоры проще использовать, потому что команды для обработки векторов – это более удобная для человека модель программирования, чем SIMD.

Структура матричной вычислительной системы

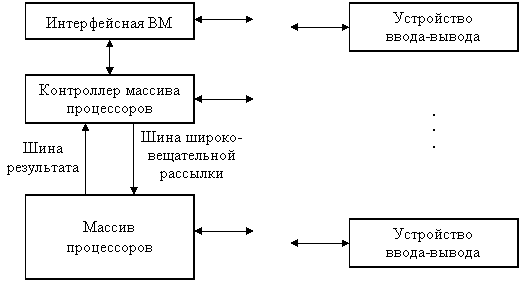

Структура матричной вычислительной системы представлена на рис. 8.1. Параллельная обработка множественных элементов данных осуществляется массивом процессоров (МПр). Единый поток команд, управляющий обработкой данных в массиве процессоров, генерируется контроллером массива процессоров (КМП). КМП выполняет последовательный программный код, реализует операции условного и безусловного переходов, транслирует в МПр команды, данные и сигналы управления. Команды обрабатываются процессорами в

|

Рис. 8.1. Обобщенная модель матричной SIMD-системы

режиме жесткой синхронизации. Сигналы управления используются для синхронизации команд и пересылок, а также для управления процессом вычислений (например определяют, какие процессоры массива должны выполнять операцию, а какие – нет). Команды, данные и сигналы управления передаются из КМП в массив процессоров по шине широковещательной рассылки. Поскольку выполнение операций условного перехода зависит от результатов вычислений, результаты обработки данных в массиве процессоров транслируются в КМП, проходя по шине результата.

Для обеспечения пользователя удобным интерфейсом при создании и отладке программ в состав подобных ВС обычно включают интерфейсную ВМ (front-end computer). В роли такой ВМ выступает универсальная вычислительная машина, на которую дополнительно возлагается задача загрузки программ и данных в КМП. Кроме того, загрузка программ и данных в КМП может производиться и напрямую с устройств ввода-вывода (например, с магнитных дисков). После загрузки КМП приступает к выполнению программы, транслируя в МПр по широковещательной шине соответствующие SIMD-команды.

Для хранения множественных наборов данных в массиве процессоров должны присутствовать и модули памяти. Кроме того, в массиве должна быть реализована сеть взаимосвязей как между процессорами, так и между процессорами и модулями памяти. Таким образом массив процессоров – это блок, состоящий из процессоров, модулей памяти и сети соединений.

Дополнительную гибкость при работе с рассматриваемой системой обеспечивает механизм маскирования, позволяющий привлекать к участию в операциях лишь определенное подмножество из входящих в массив процессоров. Маскирование реализуется как на стадии компиляции, так и на этапе выполнения. При этом процессоры, исключенные путем установки в ноль соответствующих битов маски, во время выполнения команды простаивают.

|

|