Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Использования. Классификация триггерных схем.

|

|

Триггер – электронная схема, обладающая двумя устойчивыми состояниями. Переход из одного

устойчивого состояния в другое происходит скачкообразно под воздействием управляющих

сигналов. При этом также скачкообразно изменяется уровень напряжения на выходе триггера.

Триггеры служат основой для построения регистров, счетчиков и других элементов,

обладающих функцией хранения.

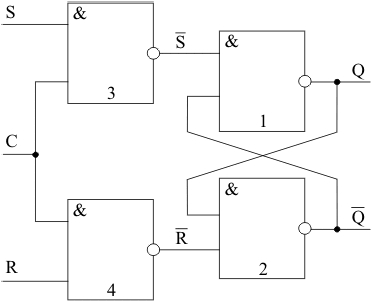

Главной частью любого триггера является запоминающая ячейка (ЗЯ). Схема запоминающей

ячейки на элементах " И-НЕ" представлена на рис. 5.

Рис. 5. Запоминающая ячейка на элементах " И-НЕ"

Входной сигнал S (Set) служит для установки ЗЯ в состояние " 1". Сигнал R (Reset)

устанавливает ЗЯ в состояние " 0" Активными значениями для них являются сигналы

низкого уровня.

Работа триггерной схемы определяется не таблицей истинности, как для комбинационной

логической схемы, а таблицей переходов. Таблица переходов показывает изменение состояния

триггера при изменении состояния входных сигналов в зависимости от его текущего состояния.

Таблица переходов запоминающей ячейки, показанной на рис. 5, представлена в табл. 3.

Таблица 3.

S R Q(t+1) Функция

00 х Запрещенная комбинация

01 1 Установка в " 1"

10 0 Установка в " 0"

1 1 Q(t) Хранение

Аналогичная запоминающая ячейка может быть построена на элементах " ИЛИ-НЕ".

|

|

Такие запоминающие ячейки можно рассматривать как простейшие асинхронные триггеры, на

базе которых строятся синхронные триггерные схемы.

Триггеры можно классифицировать по различным признакам, например так, как это показано на

рис. 6.

Рис. 6. Классификация триггерных схем

Триггер называется синхронным, если его таблица переходов хотя бы по одному

управляющему входу реализуется под воздействием синхронизирующего сигнала.

Основу синхронного одноступенчатого триггера составляет рассмотренная выше запоминающая

ячейка (элементы 1, 2). Комбинационная схема преобразует управляющие сигналы триггера, а

также, для некоторых типов триггеров, сигналы Q и Q с выходов ЗЯ в сигналы S и R на входах

запоминающей ячейки. Синхросигнал C разрешает передачу на входы элементов 1 и 2 таких

значений сигналов S и R, которые устанавливают ЗЯ в то или иное состояние. Неактивное

значение синхросигнала обеспечивает на входах запоминающей ячейки состояние управляющих

сигналов S = R = 1, что соответствует для нее режиму хранения.

Схема синхронного одноступенчатого RS-триггера приведена на рис. 8. Его таблица

переходов представлена в табл. 4.

|

Рис. 8. Синхронный одноступенчатый RS-триггер

Таблица 4.

R S Q(t+1) Функция

0 0 Q(t) Хранение

011 Установка в " 1"

100 Установка в " 0"

11 х Запрещенная комбинация

Рис. 9. Условно-графические обозначения RS-триггера с различной синхронизацией: а -

статическая синхронизация; б - статическая инверсная синхронизация; в - динамическая

синхронизация передним фронтом синхросигнала; г - динамическая синхронизация

|

|

|

Архитектура классической ЭВМ. Принципы Фон-Неймана. Назначение основных блоков.

В 1946 году Джоном Нейманом на летней сессии Пенсильванского университета был

распространен отчет, заложивший основы развития вычислительной техники на несколько

десятилетий вперед. Последующий опыт разработки ЭВМ показал правильность

основных выводов Неймана, которые, естественно, в последующие годы развивались и

уточнялись.

Основные рекомендации, предложенные Нейманом для разработчиков ЭВМ:

1. Машины на электронных элементах должны работать не в десятичной, а в

двоичной системе счисления.

2. Программа должна размещаться в одном из блоков машины – в запоминающем

устройстве (ЗУ), обладающем достаточной емкостью и соответствующими

скоростями выборки и записи команд программы.

3. Программа так же, как и числа, с которыми оперирует машина, представляется в

двоичном коде. Таким образом, по форме представления команды и числа

однотипны. Это обстоятельство приводит к следующим важным последствиям:

o промежуточные результаты вычислений, константы и другие числа могут

размещаться в том же ЗУ, что и программа;

o числовая форма записи программы позволяет машине производить

операции над величинами, которыми закодированы команды программы.

4. Трудности физической реализации ЗУ, быстродействие которого соответствовало

бы скорости работы логических схем, требует иерархической организации

памяти.

5. Арифметические устройства машины конструируются на основе схем,

выполняющих операцию сложения. Создание специальных устройств для

вычисления других операций нецелесообразно.

6. В машине используется параллельный принцип организации вычислительного

процесса (операции над словами производятся одновременно по всем разрядам).

ЭВМ, построенная по принципам, определенным Нейманом, состоит из следующих

основных блоков (рис. 1): запоминающего устройства, арифметико-логического

устройства и устройства управления.

Рис.1 Структура классической ЭВМ

|

|

Запоминающее устройство, или память – это совокупность ячеек, предназначенных для

хранения некоторого кода. Каждой из ячеек присвоен свой номер, называемый адресом.

Информацией, записанной в ячейке, могут быть как команды в машинном виде, так и

данные.

Машинная команда – это двоичный код, определяющий выполняемую операцию, адреса

используемых операндов и адрес ячейки ЗУ, по которому должен быть записан результат

выполненной операции.

Операции, определяемые кодом операции команды, выполняются в арифметико-

логическом устройстве (АЛУ).

Все действия в ЭВМ выполняются под управлением сигналов, вырабатываемых

устройством управления (УУ). Управляющие сигналы формируются на основе

информации, содержащейся в выполняемой команде, и признаков результата,

сформированных предыдущей командой (если выполняемая команда является, например,

командой условного перехода). Устройство управления помимо сигналов, определяющих

те или иные действия в различных блоках ЭВМ (например, вид операции в АЛУ или

сигнал считывания из ЗУ), формирует также адреса ячеек, по которым производится

обращение к памяти для считывания команды и операндов и записи результата

выполнения команды.

Устройство управления формирует адрес команды, которая должна быть выполнена в

данном цикле, и выдает управляющий сигнал на чтение содержимого соответствующей

ячейки запоминающего устройства. Считанная команда передается в УУ. По

информации, содержащейся в адресных полях команды, УУ формирует адреса операндов

и управляющие сигналы для их чтения из ЗУ и передачи в арифметико-логическое

устройство. После считывания операндов устройство управления по коду операции,

содержащемуся в команде, выдает в АЛУ сигналы на выполнение операции. Полученный

результат записывается в ЗУ по адресу приемника результата под управлением сигналов

записи. Признаки результата (знак, наличие переполнения, признак нуля и так далее)

поступают в устройство управления, где записываются в специальный регистр признаков.

Эта информация может использоваться при выполнении следующих команд программы,

например команд условного перехода.

Арифметико-логическое устройство. Структурная схема арифметического устройства. Временная диаграмма управляющих сигналов.

Арифметико-логическое устройство:

Классическая ЭВМ состоит из трех основных устройств: арифметико-логического

устройства, устройства управления и запоминающего устройства. Рассмотрим

особенности организации этих устройств. Прежде всего, рассмотрим структуру

арифметико-логического устройства.

В современных ЭВМ арифметико-логическое устройство не является самостоятельным

схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится

компьютер. Однако знание структуры и принципов работы АЛУ весьма важно для

понимания работы компьютера в целом. Для лучшего понимания этих вопросов проведем

синтез арифметического устройства, предназначенного для выполнения только одной

операции – умножения чисел с фиксированной запятой, заданных в прямом коде, со

старших разрядов множителя. В ходе этого процесса также обратим внимание на

особенности использования рассмотренных выше основных схемотехнических элементов

ЭВМ.

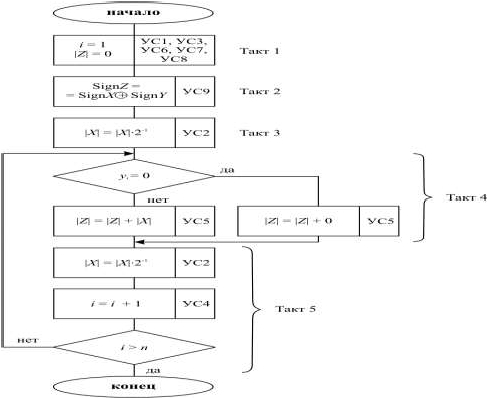

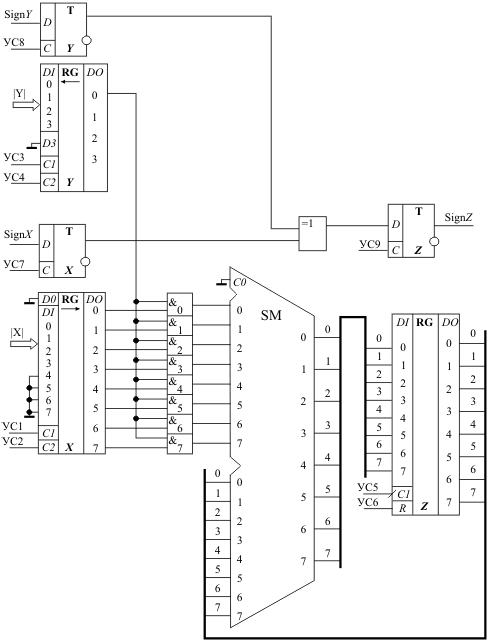

Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по

которому предполагается выполнение операции, и составить алгоритм соответствующих

действий. Исходя из алгоритма и формата исходных данных, следует определить набор

составляющих АЛУ элементов. Затем требуется определить связи между элементами,

установить порядок функционирования устройства и временную диаграмму управляющих

сигналов, которые должны быть поданы на АЛУ от устройства управления.

Пусть операнды имеют вид:

[X]пк = x0x1x2…xn

[Y]пк = y0y1y2…yn

где x0, y0 – знаковые разряды.

Операция умножения чисел с фиксированной запятой, заданных в прямом коде, со

старших разрядов множителя выполняется по следующей формуле:

Sign Z = Sign X Sign Y

|Z| = y1*|X|*2-1 + y2*|X|*2-2 + … + yn*|X|*2-n

[X]пк = 0.1101; Sign X = 0

[Y]пк = 1.1011; Sign Y = 1

Sign Z = 0 1 = 1

|X| = 0. 1 1 0 1

|Y| = 0. 1 0 1 1

y1 = 1 + 0.00000000 |Z|=0

y1 = 1 0.01101000 1 *|X|*2-1

y1 = 1 + 0.01101000 |Z|=|Z|+|X|·2-1

y2 = 0 0.00000000 0 *|X|*2-2

y1 = 1 + 0.01101000 |Z|=|Z|+0

y3 = 1 0.00011010 1 *|X|*2-3

y1 = 1 + 0.10000010 |Z|=|Z|+|X|·2-3

y4 = 1 0.00001101 1 *|X|*2-4

y1 = 1 0.10001111 |Z|=|Z|+|X|*2-4

Алгоритм вычислений представлен на рис. 2

|

|

Рис. 2. Алгоритм операции умножения чисел с фиксированной запятой, заданных в прямом коде, со

старших разрядов множителя

Каждой переменной, представленной в алгоритме, в схеме должен соответствовать

элемент хранения. Разрядность модуля произведения равна сумме разрядностей

сомножителей. Умножение двоичного числа на 2-i обеспечивается сдвигом этого числа

вправо на соответствующее количество разрядов. Переход к анализу очередного разряда

множителя (i = i + 1) может быть обеспечен сдвигом регистра множителя на один разряд в

сторону старших разрядов.

Исходя из этого, определим состав оборудования, необходимого для реализации АЛУ

заданного типа для n = 4 (таблица 1).

Таблица 1.

Сигнал

Регистр модуля

множимого RGX

Регистр модуля

множителя RGY

Регистр модуля

результата RGZ

Триггер знака

множимого TX

Триггер знака

множителя TY

Триггер знака

8 Загрузка. Сдвиг в сторону младших разрядов. УС1 УС2

4 Загрузка. Сдвиг в сторону старших разрядов. УС3 УС4

8 Загрузка. Установка в " 0". УС5 УС6

Загрузка УС7

Загрузка УС8

Загрузка УС9

результата TZ

АЛУ 8 Комбинационный сумматор –

Комбинационные схемы Получение на входе АЛУ сигналов " 0" или RGX –

в зависимости от значения yi

Структурная схема устройства представлена на рис. 3

|

|

|

Временная диаграмма управляющих сигналов, поступающих на арифметико-логическое

устройство, показана на рис. 3.1.

Рис. 3. Структурная схема арифметического устройства для выполнения операции умножения со старших

разрядов множителя чисел, заданных в прямом коде

Рис. 3.1. Временная диаграмма управляющих сигналов

Работа схемы

Такт 1. Загрузка модулей операндов в регистры RGX, RGY, а их знаков – в триггеры TX и

|

|

TY. Сброс в " 0" регистра результата RGZ.

Такт 2. Запись знака результата в триггер TZ.

Такт 3. Сдвиг регистра RGX на один разряд вправо. Через время, равное задержке на

переключение регистров и комбинационных схем, на выходе комбинационного сумматора

и, следовательно, на входе регистра RGZ устанавливается результат 0+y1· |X|·2-1.

Такт 4. Загрузка RGZ: |Z|=|Z|+y1· |X|·2-1.

Такт 5. Сдвиг RGX на 1 разряд вправо: |X| = |X|·2-1.

Сдвиг RGY на 1 разряд влево: i=i+1.

Устройство управления проверяет условие окончания операции: i > n.

Такты (6, 7), (8, 9), (10, 11)... Повтор действий тактов (4, 5) с анализом других значений yi.

В такте 10 в регистре RGZ формируется модуль произведения. Такт 11 используется лишь

для определения условия окончания операции умножения

Запоминающие устройства Классификация запоминающих устройств. Иерархическая организация памяти. Условно-графические обозначения запоминающих устройств с различной организацией.

Запоминающие устройства Классификация запоминающих устройств.

Иерархическая организация памяти. Условно-графические обозначения

запоминающих устройств с различной организацией.

Памятью ЭВМ называется совокупность устройств, служащих для запоминания,

хранения и выдачи информации.

Отдельные устройства, входящие в эту совокупность, называются запоминающими

устройствами (ЗУ) того или иного типа.

|

|