Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Организацияпроцессоров

|

|

Процессором называется устройство, непосредственно осуществляющее процесс обработки цифровой информации в ВМ и программное управление этим процессом.

Процессоры современных ВМ в большинстве случаев реализуют на одном кристалле. Соответствующую интегральную схему называют микропроцессором.

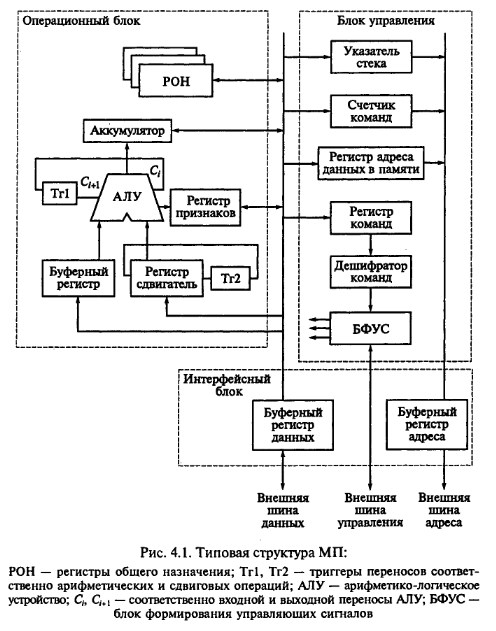

В самом общем случае функциональную схему МП можно представить в виде композиции трех функциональных блоков: операционного блока (ОБ), блока управления и интерфейсного блока (рис. 4.1). Кроме них в состав микропроцессора могут входить и некоторые другие блоки, участвующие в организации вычислительного процесса, например, блок прерывания, блок защиты памяти, блоки контроля, диагностики и др.

Операционныйблок ( ОБ ). Предназначен для выполнения некоторого функционально полного набора логических и арифметических операций. Как правило, в его состав входят АЛУ, буферные регистры операндов, регистр результата (аккумулятор), регистр признаков и блок регистров общего назначения (РОН).

В АЛУ выполняются несколько простейших арифметических (сложение, вычитание) и поразрядных логических (И, ИЛИ, НЕ и др.) операций. Операции по обработке данных, для которых в ОБ отсутствуют аппаратные средства, выполняют программно с помощью процедур. Такие процедуры реализуются в виде последовательности простых операций ОБ, т.е. выполняются на более высоком уровне организации вычислительного процесса.

Кроме универсального АЛУ МП может содержать одно или несколько специализированных АЛУ. В качестве последних обычно используют блоки аппаратного умножения и деления, а также блоки для выполнения операций с плавающей точкой.

Важной составляющей ОБ современных МП является блок внутренней памяти, реализованный в виде набора программно доступных регистров, называемых регистрами общего назначения (РОН).

Время обращения к РОН меньше, чем к любым другим устройствам памяти, поэтому память на РОН называется сверхоперативной, а устройство, в виде которого она реализована, — сверхоперативным запоминающим устройством (СОЗУ).

Число, назначение и разрядность регистров блока РОН в различных МП могут существенно отличаться. В использовании РОН имеются два крайних подхода. При первом подходе, реализуемом в МП компании Motorola, почти все регистры МП выполняют абсолютно одинаковые функции, т.е. являются универсальными и взаимозаменяемыми. При втором подходе, характерном для МП компании Intel, многие регистры наряду с возможностью использования в качестве универсальных в некоторых командах могут выполнять специфические функции, закрепленные за этими регистрами.

В большинстве ранних моделей МП один из общих регистров выделялся в качестве главного регистра. Наделение главного регистра, называемого аккумулятором, или регистром результата, особыми функциями позволяло реализовать ОБ в виде одноадресного устройства. В таком ОБ один из исходных операндов арифметических и логических операций обязательно должен размешаться в аккумуляторе и в него же помешается результат. Другой операнд названных операций может находиться в памяти или РОН. Входные данные поступают в аккумулятор с внутренней шины МП, а аккумулятор, в свою очередь, может посылать данные на эту шину.

Функциональные возможности ОБ, содержащего аккумулятор, достаточно широки. С его помощью можно реализовать различные операции. Рассмотрим основные микрооперации, с использованием которых реализуется выполнение операций (команд).

• Содержимое любого РОН или ячейки памяти по внутренней шине данных может быть передано через аккумулятор в буферный регистр или напрямую в регистрсдвигатель.

• АЛУ обеспечивает выполнение арифметических и логических операций над содержимым регистра-сдвигателя и буферного регистра с записью результата в аккумулятор, а признаков — в регистр признаков.

• Из аккумулятора результат операции может быть передан в любой РОН или ячейку памяти.

• Операция сдвига содержимого любого РОН выполняется последовательно передачей слова из РОН в сдвигающийрегистр, сдвига этого слова и последующей записи преобразованного слова в тот же регистр РОН.

• Операции над словами с повышенной разрядностью реализуются путем программно последовательной обработки отдельных частей многоразрядных слов. Для обеспечения возможности обработки данных с разрядностью, превышающей разрядность АЛУ и регистров, в структуре ОБ, предусмотрены два дополнительных триггера: Trl и Тг2. С их помощью осуществляется запоминание сигналов арифметического переноса из АЛУ и выходного бита переноса регистра сдвига. Например, с помощью 8-разрядного МП сравнительно просто осуществляется арифметическая обработка 24-разрядных слов. Для этого выполняют три цикла обработки 8-разрядных частей этих слов.

• Признаки операций АЛУ (флаги), характеризующие результаты вычислений, запоминаются в одноименных флагахрегистра признаков. Типичными признаками являются: нулевой результат, наличие переноса, переполнение, четность, знак и некоторые другие.

Блокуправления. В процессе выполнения программы блок управления (см. рис. 4.1) координирует работу всех блоков МП и микропроцессорной системы в целом. С помощью блока управления формируются управляющие сигналы, необходимые для организации обмена информацией с внешними устройствами, и обеспечивается выборка команд программы из памяти. В целом блок управления выполняет следующие действия:

• считывает и запоминает текущую команду;

• формирует адрес следующей команды;

• реализует выполнение по тактам алгоритма поступившей команды;

• управляет обменом информацией с внешними устройствами по системной шине.

Блок управления состоит из регистра команд (РгК), дешифратора команд (ДшК) и блока формирования управляющих сигналов (БФУС). Управляющие сигналы с выходов БФУС поступают на управляющие входы других блоков МП, настраивая их на выполнение определенных микроопераций. В состав блока управления также включают программно доступные счетчик команд Instruction Pointer — указатель команд IP и указатель стека SP (Stack Pointer).

Выполнение любой команды реализуется как последовательность трех фаз: выборка, декодирование и выполнение.

Фазавыборки обеспечивает считывание очередной команды из памяти и пересылку ее в МП. Адрес считываемой команды определяется содержимым программного счетчика PC.

Код операции текущей команды запоминается в РгК. В фазедекодирования содержимое РгК с помощью ДшК преобразуется в управляющее слово. Схема синхронизации, используя это слово, вырабатывает совокупность сигналов, управляющих внутренними операциями МП и обменом информацией между МП и внешними устройствами.

После выборки и дешифрирования команды ОБ в декодированном виде получает информацию о том, какую операцию он должен выполнить, где в памяти расположены данные, куда следует направить результат операции и где расположена следующая команда. В фазевыполненияБФУС вырабатывает последовательности управляющих сигналов, обеспечивающих выполнение операции, заданной в команде.

Каждый блок за один такт может выполнить простейшую операцию (для регистра — это запись кода или выдача хранимого кода на выходы, для счетчика — запись кода в счетчик, прибавление или вычитание единицы, выдача хранимого кода, для мультиплексора — передача на выход сигнала с входа, определяемого управляющим кодом, для АЛУ — одна из простейших операций, которая выполняется на уровне регистровых передач: сложение, вычитание, сдвиг, реализация одной из поразрядных логических операций).

Элементарное действие, выполняемое в одном из узлов ОБ в течение одного такта, называется микрооперацией. В некоторые такты в различных узлах ОБ (регистрах, мультиплексорах, счетчиках и др.) одновременно могут выполняться несколько микроопераций. Настройка ОБ на выполнение одной из возможных микроопераций осуществляется с помощью сигналов, поступающих на его управляющие входы. Набор этих сигналов (вектор сигналов управления) вырабатывается БФУС.

Совокупность одновременно выполняемых микроопераций соответствует микрокоманде.

Команда в общем случае состоит из нескольких простейших действий и обычно выполняется за несколько тактов, т.е. требует для своего выполнения нескольких микрокоманд. Последовательность микрокоманд, обеспечивающая выполнение команды, называется микропрограммойкоманды.

Управляющий автомат, формирующий наборы управляющих сигналов для микропрограммой команды, называют микропрограммным автоматом (МПА). МПА подразделяют на аппарат с «жесткой» логикой управления и с «мягкой» логикой управления.

МПА с «жесткой» логикой управления представляется в виде конечного автомата (в сложных случаях используется сеть конечных автоматов). Алгоритм команды в МП с подобным МПА задан жестко соединениями схемы, поэтому список операций (система команд) МП является неизменным, и это не позволяет вносить какие-либо изменения в систему команд МП после его изготовления. Основным достоинством МПА с «жесткой» логикой управления является его высокое быстродействие. Такие устройства управления используются в большинстве однокристальных МП, отличительной характеристикой которых является то, что все элементы структуры МП выполнены на одном кристалле.

При реализации МПА с «мягкой» логикой управления используется типовая структура автомата с блоком памяти микропрограмм, который, как и основная память, имеет линейно-адресную организацию. В целом разработка УА МПА с «мягкой» логикой управления в значительной мере определяется разработкой микропрограмм команд.

В современных МП в зависимости от системы команд и сложности алгоритмов микропрограмм команд используются оба подхода при построении МПА. На уровне регистровых передач с помощью МПА независимо от типа управления непосредственно осуществляется интерпретация машинных команд программы и их выполнение. Именно поэтому уровень регистровых передач также называют микропрограммным уровнем организации вычислительных процессов ВМ.

Интерфейсныйблок. Предназначен для организации взаимодействия МП с памятью и устройствами ввода-вывода, расположенными на системной шине процессора, а также для обмена данными между ОБ и внутренними устройствами МП. Непосредственное подсоединение устройств ввода-вывода к МП осуществляется с помощью специальных схем сопряжения, которые называются интерфейсомвводавывода. В общем случае интерфейсный блок процессора должен выполнять следующие функции:

• формировать выходные сигналы на шинах адреса, данных и управления в режиме вывода;

• формировать выходные сигналы адреса и управления и считывать (воспринимать) сигналы с шины данных в режиме ввода;

• синхронизировать процессы внутри процессора и на системной шине;

• реализовывать стандартный для системной шины протокол обмена.

Системная шина объединяет сигналы шин данных, адреса и управления. Протокол обмена информацией по СШ определяет последовательности сигналов (временную диаграмму сигналов в шине), обеспечивающих правильную передачу информации между устройствами микропроцессорной системы. Взаимодействие по шине осуществляется за цикл шины. Длительность цикла шины может изменяться в зависимости от быстродействия внешних устройств.

Для согласования по быстродействию взаимодействующих при обмене по шине устройств используется принципквитирования - процессор, управляющий обменом, в каждом цикле ждет уведомления (квитанции) о том, что устройство на шине выполнило операции, связанные с обменом, т.е. выставило на шину данные при вводе либо восприняло данные с шины при выводе.

|

|