Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Типовая структура машинной команды

|

|

► Структура машинной команды " в пространстве"

| Структура команды: | КОП | Адресная часть |

Машинная команда во внутреннем представлении по форме представляет собой двоичное слово, состоящее из двух частей (полей):

● кода операции (КОП) и

● адресной части команды.

Код операции обозначает, что должна сделать команда. Длина битового поля, отведенного в команде под КОП, должна быть достаточной для кодирования всех команд процессора.

Поле КОП может быть переменной или постоянной длины. Некоторые кодовые комбинации поля КОП оставляют незадействованными, это резервные коды для будущего расширения системы команд.

Адресная часть команды содержит информацию о местоположении одного или нескольких операндов, используемых командой. Операнды или данные в ЭВМ, с которыми машинные команды выполняют действия по форме также представляют собой двоичные слова. Эти битовые слова часто (но отнюдь не всегда) имеет смысл интерпретировать как числа.

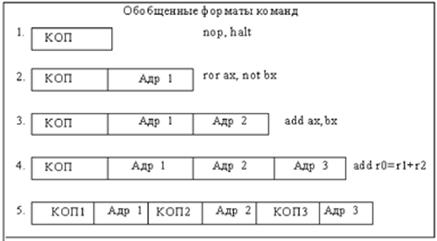

Можно выделить несколько обобщенных форматов команд на основе рассмотрения сколько операндов и адресных частей в команде (см. Рис. 13).

Рис. 13 Обобщенные форматы команд

● В любой системе команд есть " пустая" команда, которая не делает никакого действия (NOP). Для нее просто не требуется указания операндов. Некоторые команды не требуют указания каких-либо операндов, так как их действие направлено на один заранее предопределенный операнд. Например, команда " разрешить прерывание " STI - эта команда устанавливает бит IF в регистре состояний EFLAGS.

● Некоторые команды выполняют действие с одним операндом. Такие команды называют о днооперандными. В таких командах есть одно адресное поле для указания места расположения (или значения) операнда.

Передача управления – также однооперандная команда, в которой результат операции – изменение содержимого счетчика команд:

neg ax; эта команда изменит знак целого числа в регистре процессора.

● В процессоре есть команды пересылок, которые копируют содержимое элементов памяти в другие элементы памяти. Они требуют указания двух операндов: источника Source (Src) и приемника Destination (Dest, Dst).

Пример: mov bl, [esi] - содержимое однобайтового элемента данных из ячейки памяти, адрес которой хранится в регистре процессора esi, копируется в регистр процессора bl.

● Арифметические действия (сложение, вычитание, умножение) оперируют с двумя операндами и формируют результат операции: C=A+B.

В некоторых системах команд соответствующие команды позволяют программисту независимо указать места расположения всех трех элементов.

Для уменьшения длины команды в других системах команд эти команды имеют только два адресных поля, при выполнении команды результат операции помещается на место одного из операндов, замещая его.

● В системах команд процессоров с длинным командным словом (VLIW) одновременно выполняются несколько команд и они должны быть записаны подряд - длинным словом. Формировать длинное слово может или программист (в сигнальных процессорах), или транслятор языка (Itanium).

Т.о. структура адресной части команды может существенно различаться для разных команд как по количеству описываемых операндов, так и по способу кодирования информации о том, где расположен операнд.

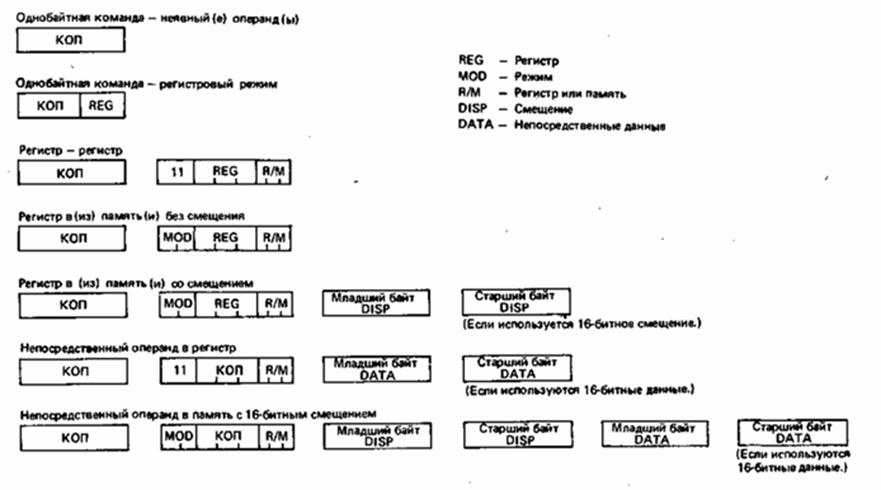

Примеры форматов команд микропроцессора 8086

Разработчики системы команд выбирают структуру адресной части команды, исходя из нескольких взаимноисключающих требований, но главное:

● Адресная часть команды должна быть по возможности короткой, чтобы не увеличивалась чрезмерно длина команды.

● Должна обеспечиваться достаточная гибкость и универсальность кодирования параметров команды.

Адрес(а) операнда(ов), с которым(и) выполнит действие команда, определяются в процессе обработки этой команды (формируются устройством вычисления адресов). Такой адрес называют исполнительным (executive) или эффективным (effective) адресом ЕА.

Адрес, который передается по магистрали из процессора в ОЗУ и управляет работой ОЗУ - физический адрес. Для того, чтобы получить значение физического адреса из значения исполнительного адреса, последний в процессоре должен быть подвергнут преобразованию, которое обозначают словосочетанием трансляция адреса.

Понятие адресного пространства является одним из фундаментальных в организации ЭВМ.

● Физическое адресное пространство - пространство реально формируемых адресов, которым могут соответствовать реально существующие (включенные в систему) элементы памяти. В х86 может быть сформирован физический адрес длиной 32 бита, т.е. физическое адресное пространство равно 232.

Трансляция адреса это операция отображения одного адресного пространства (или может быть его части) на другое адресное пространство (или его часть).

В простейших вычислительных системах трансляция адресов может представлять собой просто тождественное отображение, т.е. физический адрес равен исполнительному.

Процедура вычисления физического адреса по содержимому адресной части команды может быть достаточно сложной.

Она включает два этапа:

1) вычисление исполнительного/эффективного адреса ЕА (executive/ effective address) в соответствии со способом адресации;

2) переход от ЕА к физическому адресу (эта часть вычислений, как уже было сказано, называется трансляцией адреса).

► Структура команды во времени

Процесс выполнения одной машинной команды может быть разложен на несколько этапов. Разбиение на этапы имеет методическое назначение - оно помогает понять, как взаимодействуют отдельные узлы процессора при выполнении команд.

Однако разбиение процесса выполнения команды на отдельные более мелкие этапы при конструировании внутренней структуры и схемотехники процессора позволяет использовать конвейеризацию для увеличения быстродействия процессора структурным путем. Фактически в разных процессорах количество этапов, на которые разбит процесс выполнения команд, может различаться как для разных процессоров, так и для разных команд в одном процессоре.

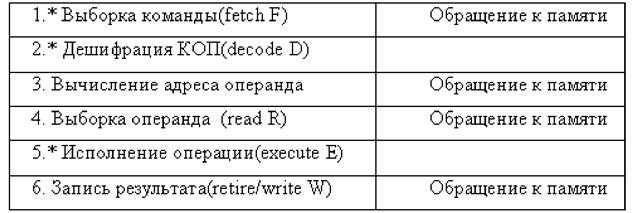

Процесс выполнения команды может содержать следующие этапы:

Опишем более подробно процесс выполнения команд программы.

1. Выборка (F1 Fetch). Процессор байт за байтом считывает из ОЗУ порции программного кода (фрагмент программного кода, соответствующий команде процессора обязательно содержит КОП, и, возможно, но необязательно адресную часть) по адресу, который в данный момент содержится в счетчике команд.

После считывания очередной порции программного кода, содержимое счетчика автоматически увеличивается, так, что он всегда содержит адрес байта программы, который должен быть считан следующим.

2. Декодирование (D2 Decode). Процессор декодирует команду - анализирует считанный КОП, и по типу операции, закодированному в КОП, принимает решение о том, какая операция должна быть выполнена (управление АЛУ), а также о том, сколько байтов содержит данная команда и как их следует интерпретировать. Затем следует декодирование адресной части (если она есть). Если декодируемая команда предполагает расположение операнда в памяти, следует этап A3, в противном случае (если операнды расположены только в регистрах процессора) этап A3 отсутствует.

3. Вычисление исполнительного адреса (A3 Address Calculation), в ходе которого процессор формирует физический адрес операнда в памяти.

Иногда для определения составных частей адреса операнда необходимо дополнительное обращение к ОЗУ. По вычисленному адресу происходит затем следующий этап R4.

4.Выборка операнда (R4 Read), для чего (возможно) придется выполнить обращение к ОЗУ. Если адресная часть команды содержит информацию о нескольких операндах, находящихся в памяти, то этапы A3 и R4 будут повторены нужное количество раз. Если операнды располагаются в регистрах процессора, то на этапе R4 обращений к памяти не требуется. За выборкой операндов следует этап E5:

5. Исполнение операции (E5 Execute) - не предполагает обращения к памяти, хотя время выполнения может для разных команд значительно различаться. По окончании этапа исполнения, может быть (но не всегда) придется произвести заключительное действие W6:

6. Запись результата (W6 Write) для чего (возможно) потребуется обращение к ОЗУ.

В зависимости от вида операции, количества операндов, способов адресации структура команды во времени может сильно различаться для различных команд. Это означает, что для разных команд некоторые этапы могут отсутствовать и для разных команд длительность во времени (даже одноименных) этапов может быть различной. Это замечание окажется существенным, когда будем говорить о возможностях конвейеризации - параллельного одновременного выполнения разных этапов разных команд. Чтобы такое запараллеливание стало возможным, в процессоре необходимо иметь для выполнения каждого из этапов отдельный исполнительный узел.

|

|