Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Реальный режим

|

|

Реальный режим процессоров IA-32 — это режим генерирования адресов, используемый процессором 8086. В нем память рассматривается как последовательность сегментов объемом по 64 Кбайт. Для каждого сегмента 16-разрядные исполнительные адреса формируются с использованием режимов адресации процессора 8086. Для доступа к сегментам кода, стека и двум сегментам данных в этом процессоре применяются сегментные регистры CS, SS, DSиES. В процессор 80386 были включены еще два сегментных регистра —FSиGS.

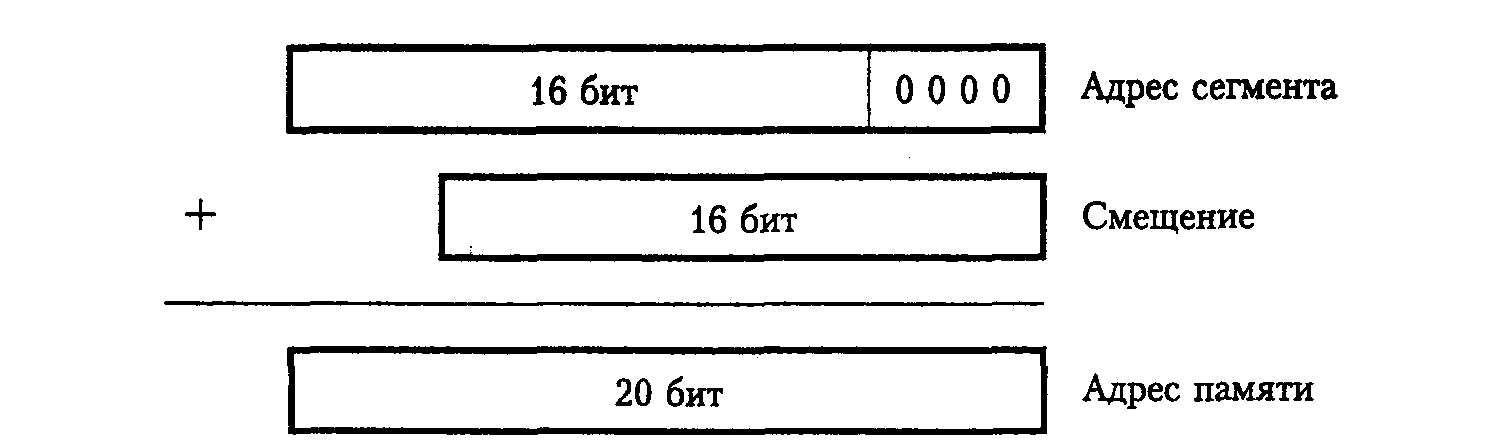

На рис. 9.6.1 представлен процесс генерирования 20-разрядных внешних адресов памяти. Заданное в сегментном регистре 16-разрядное значение сдвигается на четыре позиции влево, вследствие чего получается 20-разрядный адрес памяти, представляющий собой начальный адрес сегмента. Для получения 2-разрядного исполнительного адреса к начальному адресу сегмента добавляется сгенерированный процессором 16-разрядный исполнительный адрес, обозначенный на рисунке как смещение.

Чтобы локализовать в памяти сегмент, в сегментный регистр помещаются 16 старших разрядов 20-разрядного адреса начала этого сегмента. В адресном пространстве, занимающем 1 Мбайт и покрываемом 20-разрядными адресами, может располагаться 16 неперекрывающихся сегментов объемом 64 Кбайт. Однако сегменты могут и перекрываться. Это удобно при организации совместного доступа к командам и данным разными программами. Сегменты CS и SSиспользуются в тех случаях, когда в программе имеются ссылки на команды или стек. Для хранения данных по умолчанию выделяется сегментный регистрDS. Если же для доступа к данным команды должен применяться регистрES, в начало этой команды добавляется соответствующий код.

Рис. 9.6.1. Формирование адреса памяти в процессоре 8086

|

|