Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Порівняння інерційних і транспортних затримок

|

|

Моделі інерційної і транспортної затримки є достатніми для опису у VHDL довільної

фізичної системи. Вони мають наступні головні подібності та відмінності:

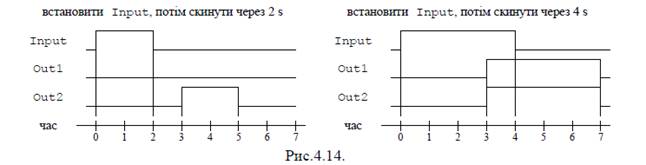

· Інерційна затримка

є затримкою за замовчуванням у VHDL і не вимагає ніяких додаткових декларацій не поширює імпульси, коротші ніж задана затримка

Не поширює імпульси, коротші ніж задана затримка

· Транспортна затримка

Вимагає використання ключового слова transport.

поширює всі зміни вхідного сигналу, незалежно від того, як швидко і як часто вони відбуваються

· Обидва

описується за допомогою оператора after після якого вказується значення часу

може застосовуватись до сигналів довільного типу

Out1 < = Input after 3 s;

Out2 < = transport Input after 3 s;

Концепція дельта-затримок

Найпростіший оператор присвоєння сигналу (без затримки) складається з цільового сигналу

та виразу, що визначає його значення. Таке присвоєння визначає, що значення виразу буде

присвоєне сигналу через час дельта. Фізично цей час дорівнює нулю, але з точки зору обробки

значень сигналів він ненульовий, тобто є логічним Наприклад, присвоєння, яке має відбутися

через час, рівний двом дельтам, буде виконане після присвоєння, що має відбутися через одну

дельту, при цьому результат більш пізнього присвоєння недоступний для більш ранніх присвоєнь.

Однак обидва присвоєння відбудуться скоріше, ніж пройде найменший фізичний інтервал часу.

Іншими словами, на протязі будь-якого фізичного інтервалу часу може бути довільна кількість

дельта-інтервалів.

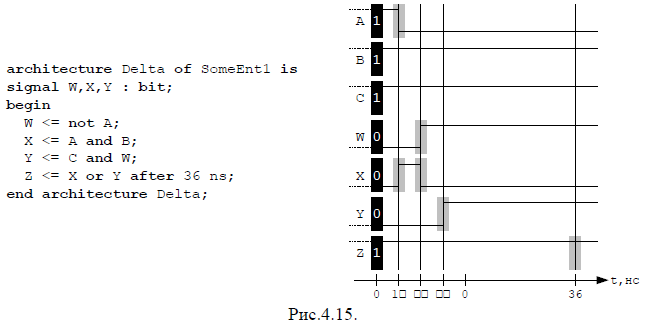

В наступному описі використовуються оператори присвоєння з нульовими затримками для

внутрішніх вузлів схеми та затримане присвоєння для виходу Z із затримкою 36 наносекунд.

Припустимо, що зовнішні сигнали A, B і C проініціалізовані значенням ‘1’, отже їх значення

перед моментом 0 та в момент 0 рівні ‘1’. Припустимо також, що зовнішній для цього опису

сигнал A в момент 0 приймає значення ‘0’. Оскільки A – сигнал, це нове значення з’явиться

пізніше, через дельта-інтервал в момент 1δ. Через один дельта-інтервал після зміни значення A

нові значення отримають вузли W та X, отже W стає рівним ‘1’ (значення not A), а X стає рівним ‘0’

(значення A and B) в момент 2δ. Подія з X приводить до присвоєння нульового значення виходу Z

через 36 наносекунд. Подія з W приводить до переобчислення виразу для Y і як результат – до

зміни значення вузла Y через один дельта-інтервал після зміни W; це значення змінюється з ‘0’ в

‘1’ в момент 3δ. Після цього подія з Y приводить до переобчислення вихідного виразу,

результатом якого знову буде присвоєння нового значення виходу через 36 наносекунд після цієї

події.

Друге присвоєння виходу Z відмінює попереднє, і оскільки значення Z вже дорівнює ‘1’,

воно не спричинює події на цій лінії. Оскільки встановлений стан значення Z є правильним,

проміжні значеня Z не моделюються у відповідності до реальної схеми. Необхідно зауважити, що

події, які виникають на X і Y в момент 0, не транслюються на вихід Z через 36 наносекунд. Це

пов’язано з тим, що фізична затримка часу зглажує всі дельта-затримки.

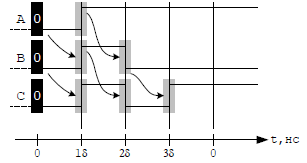

Наступний опис наведено для кола з двох послідовно включених інверторів з нульовими

затримками, де A – це вхід, C – вихід, а B – проміжна точка. Сигнали A, B і C ініціалізуються

значенням ‘0’. Сигналу A присвоюється значення ‘1’, і це спричинює зміну сигналу B,

переключення якого генерує зміну для C.

Часова діаграма демонструє, що всі зміни сталися в момент 0 між 0+1δ та 0+3δ. Кожна зміна

приводить до події. В момент 0 сигнали A, B і C мають значення, визначені в декларації сигналів.

В той час, коли ‘1’ присвоюється A, інверсія A, значення якого все ще рівне ‘0’ в момент 0,

присвоюється B. Також в момент 0, інверсія сигналу B, значення якого все ще рівне ‘0’,

присвоюється сигналу C. Через один дельта-інтервал в 1δ сигнали A, B і C отримають нові

значення, які всі рівні ‘1’. Нове значення A генерує присвоєння для B через один дельта-інтервал в

2δ, що спричинює подію зміни значення B на ‘0’. Аналогічно, значення B в 1δ спричинює подію

для C в 2δ. Подія з B в момент 2δ приводить до переобчислення виразу оператора присвоєння для

C, що в свою чергу приводить до ще однієї події з C через один дельта-інтервал в 3δ.

architecture Delta of SomeEnt2 is

signal A, B, C: bit: = '0';

begin

A < = '1';

B < = not A;

C < = not B;

end architecture Delta;

Таким чином, дельта-затримки є логічними затримками і використовуються для визначення

послідовності виконання одночасних подій.

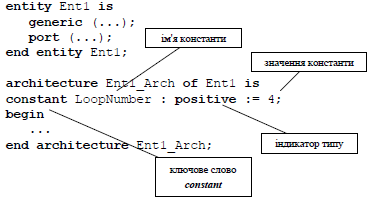

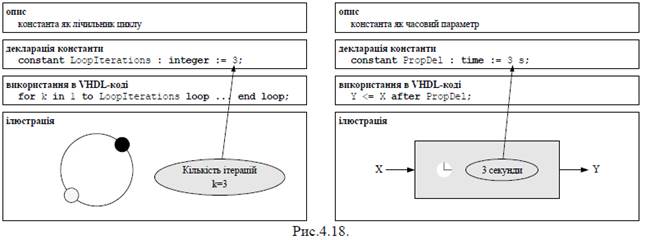

Константи

Декларування констант

Константи відіграють ту саму роль, що і параметри: вони забезпечують статичну

інформацію, яка може використовуватись всередині моделі. Однак, на відміну від параметрів

(generics), що декларуються всередині інтерфейсів, константи декларуються всередині

архітектур.

Декларація констант складається з наступних елементів:

• ключове слово constant,

• ім’я константи (ідентифікатор константи),

• символ ‘: ’,

· індикатор типу константи,

· значення константи, задане після символа ‘: =’,

· символ ‘; ’, яким закінчується рядок.

Якщо дві або більше констант мають однаковий тип і однакове значення, вони можуть бути

описані в одній декларації.

В деяких особливих випадках присвоєння значення константі може бути відкладене.

Використання констант

Головна мета використання констант полягає у використанні “зрозумілих імен” із

зрозумілими визначеннями типів замість так званих “жорстко-кодованих” літеральних значень.

При цьому код стає більш читабельним і простим у використанні, оскільки зміна константи в

одному місці впливає на всі її входження в усій архітектурі. Якщо ж використовуються жорстко-

кодовані значення, користувач повинен уважно перевірити весь опис рядок за рядком для того,

щоби переконатись, що всі значення виправлені.

Взагалі константи використовуються так само, як параметри. Вони застосовуються зокрема

для:

• опису розміру складних об’єктів (таких як масиви і шини);

• керування лічильниками циклів;

• визначення часових параметрів: затримок, часу встановлення, часу припинення, часу

переключення, та ін.

Оскільки константи декларуються в архітектурах, вони не можуть використовуватись для

визначення розміру векторів, задекларованих як порти в інтерфейсах. Однак, це обмеження можна

обійти, якщо константа декларується в пакеті, що використовується інтерфейсом.

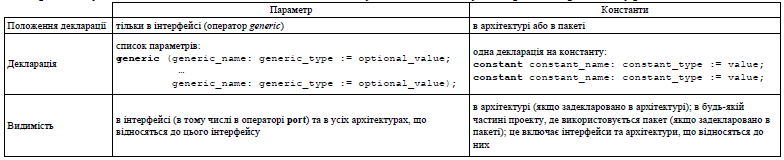

Порівняння констант і параметрів

Може виникнути питання, навіщо VHDL містить дві такі подібні конструкції, як параметри і

константи?

Головна відмінність між параметрами і константами полягає в тому, що параметри можуть

використовуватись динамічно, а константи є виключно статичними. Це означає, що можна

змінювати значення параметрів без будь-яких змін коду. З іншого боку, константи не можуть бути

змінені без зміни коду. Це важливо особливо в тому випадку, коли специфікація використовується

як компонент для опису на вищому рівні. Кожний раз при використанні такого компонента для

нього можуть бути задані інші значення параметрів, якщо вони описані як параметри.

Інший аспект полягає в наступному. Один і той самий інтерфейс може використовуватись

декількома архітектурами і усі параметри застосовуються до всіх архітектур інтерфейсу. Будь-яка

зміна значення параметра впливає на всі його входження у всіх архітектурах. Якщо ж

використовуються константи, їх зміни локалізуються лише у вибраній архітектурі.

5. Опис поведінки системи у VHDL:

процеси, змінні, керування послідовністю виконання операторів.

Процеси

Опис поведінки

Головна мета будь-якої електронної ситеми або пристрою – трансформувати вхідні дані у

вихідні результати. Такий тип діяльності називається “поведінкою” або “функціонуванням”

системи, і опис системи задає порядок перетворення вхідних даних у вихідні результати.

Поведінковий опис є списком операцій, які повинні бути виконані для отримання очікуваних

результатів.

машинний код

if event_occurred then buttons: = " enabled"

if button1_pressed then output_result1

else if button2_pressed then output_result2

else output_result3

buttons: = " disabled"

Рис.5.1.

Що таке процес?

Результат в попередньому прикладі залежить від послідовності операцій. Це дуже типово для

більшості описів проектів. Коли хтось виконує процедуру для виконання чогось, він надає список

дій, які повинні бути виконані послідовно крок за кроком.

Процес – це формальний шлях для виконання таких послідовних операцій. Він має дуже

структурований формат, навіть якщо ним представлено поведінку тільки незначної частини

проекту.

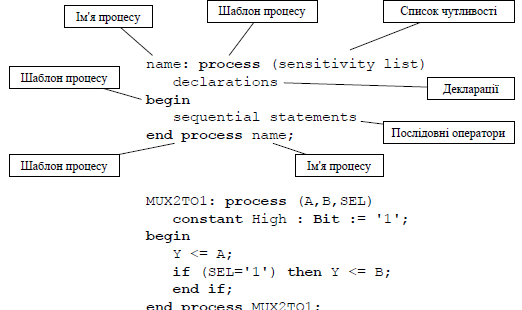

Структура процесу

Процес декларується за допомогою ключового слова process. Для покращення читабельності

можна надати процесу ім’я. Таке ім’я повинно стояти перед ключовим словом process і

закінчуватись двокрапкою. Це ж ім’я може бути повторене в кінці, відразу після оператора end

process, але без двокрапки.

Процес – це послідовність операцій (операторів). Список операторів процесу починається з

ключового слова begin і закінчується ключовими словами end process, після яких вказується ім’я

процесу, якщо таке є.

Ключове слово begin вживається для того, щоби відокремити послідовні операції від

декларацій змінних та констант. Воно вказується відразу після декларацій і перед списком

послідовних операцій.

Ім’я процесу є необов’язковим і, якщо задане, повинне передувати ключовому слову process і

відокремлюватись від нього двокрапкою. Це ім’я може бути повторене в кінці процесу,

відразу після оператора end process, але без двокрапок.

Шаблон процесу містить три елементи, які містить кожний процес: ключове слово process на

початку процесу, ключове слово begin на початку операторної частини і оператор end process

в кінці процесу. Слід зауважити, що після перших двох операторів крапка з комою не

ставляться.

Список чутливості. Виконання припиненого процесу може бути поновлено, коли один з сигналів

його списку чутливості змінить своє значення. Поновлення та припинення процесів буде

розглянуто далі.

Декларації. Всі декларації процесу розміщуються після заголовку процесу і перед ключовим

словом begin. Всі об’єкти, задекларовані всередині процесу, видимі тільки в цьому процесі.

Сигнали не можуть декларуватись всередині процесу.

Послідовні оператори. Всі оператори в процесі, описані між ключовими словами begin і end

process виконуються послідовно.

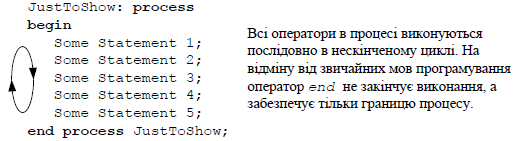

Виконання процесу

В процесі після виконання останнього оператора виконується негайний перехід на виконання

першого оператора. Таким чином, процес ніколи не закінчується.

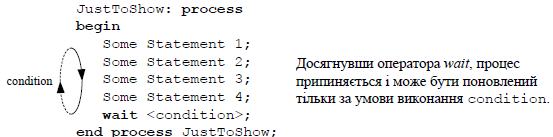

Оператор wait

Реальні електронні пристрої працюють в нескінченому циклі, і після їх активації виконують

внесені в список задачі, після чого повертаються в стан “очікування певної умови”. Іншими

словами, пристрій припиняє дії після того, як закінчує біжучу задачу, і поновлює дії після того, як

знову виникнуть певні умови.

Така робота пристроїв описується у VHDL оператором wait. Він використовується для

• безумовної зупинки (припинення) виконання процесу;

• задавання списку умов, що можуть поновити процес.

Якщо процес містить оператор wait, він виконує послідовно всі оператори до оператора wait.

Після цього процес припиняється і очікує виконання умови, заданої в операторі wait. Як тільки це

відбувається, процес поновлюється і виконує всі оператори, поки знову не зустріне оператор wait.

Типи оператора wait

В зв’язку з тим, що в реальних аплікаціях процес може бути поновлений з різних умов, у

VHDL є три типи оператора wait: очікування на протязі певного часу, очікування виконання

деякого логічного виразу і очікування зміни значення сигналу. Ці три типи конструкцій мають

наступні форми:

• wait for time_expression,

• wait until condition,

• wait on sensitivity_list.

Якщо змішуються декілька таких умов, вони утворюють четверту конструкцію, яка

називається складною умовою.

• wait for time_expression

Припиняє процес на визначений час. Час може бути заданий безпосередньо, або як

вираз, результатом якого є значення часу. Використовуються в основному для

моделювання на тестових стендах.

wait for 10 ns;

wait for ClkPeriod / 2;

• wait until condition

Припиняє процес доти, доки задана умова не стане істинною завдяки зміні будь-якого

сигналу, що містяться в умові. При цьому, якщо сигнал не змінюється, wait until не

поновить процес, навіть якщо сигнал задовільняє умову.

wait until Clk='1' for 10 ns;

wait until CE and (not RST);

wait until IntData > 16;

• wait on sensivity_list

Припиняє процес доти, доки не відбудеться подія з будь-яким з сигналів, вказаних в

списку чутливості. Іншими словами, процес поновлюється тільки тоді, коли зміниться

значення хоча б одного сигналу з списку чутливості.

wait on CLK;

wait on Enable, Data;

• складний wait

Містить комбінацію двох або трьох різних форм оператора wait.

wait on Data until CLK='1';

wait on sensitivity_list

Якщо симулятор знаходить оператор wait відразу на початку процесу, то процес буде

негайно припинений і жодний оператор не буде виконаний. Якщо ж оператор wait розташований

ближче до кінця процесу, деякі оператори будуть виконані, перш ніж процес буде припинений.

Оператор wait може розташовуватись в процесі будь-де. Але, як правило, він

використовується або в кінці процесу, або на початку. Дозволяється також використання кількох

операторів wait в процесі, що часто застосовується у тестових стендах.

process

begin

wait on SigA;

somestatement1;

somestatement2;

somestatement3;

end process;

Якщо оператор wait є першим оператором

процесу, процес буде припинений відразу

після старту.

process

begin

somestatement1;

somestatement2;

somestatement3;

wait on SigB;

end process;

Якщо оператор wait є останнім оператором

процесу, всі оператори будуть виконані один

раз, після чого процес буде припинений.

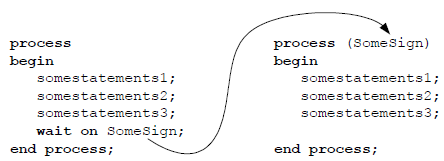

Список чутливості процеса

Очікування за списком чутливості, тобто очікування зміни значення сигналу, найчастіше

використовується в якості умови поновлення процесів. У VHDL застосовується конструкція, яка

називається списком чутливості процесу. Цей список вказується відразу після ключового слова

process і повністю відповідає оператору wait on sensitivity_list в кінці процесу.

Процес із списком чутливості не може містити явних операторів wait.

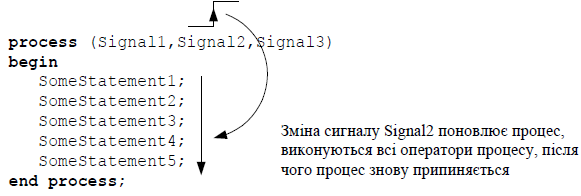

Коли починається симуляція, процес із списком чутливості виконується один раз, оскільки

список чутливості еквівалентний оператору wait в кінці процесу, і після цього процес

припиняється. Процес буде припиненим доти, доки будь-який сигнал з його списку чутливості не

змінить свого значення. Така зміна поновлює процес і всі оператори процесу, з початку до кінця,

будуть послідовно виконані. Під словом “всі” слід розуміти всі оператори процесу, а не тільки ті,

що мають відношення до сигналу, який поновлює процес. Після того, як буде виконаний останній

оператор, процес знову буде припинений.

Змінні

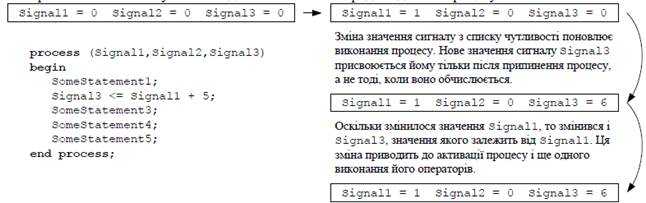

Сигнали в процесах

Головна мета поведінкового VHDL-опису – задати реакцію виходів на зміну входів. Як

входи, так і виходи є сигналами, отже реакція вихідних сигналів представляється як присвоєння

сигналів. Сигнали і присвоєння сигналів використовуються всередині процесів. Однак,

використання сигналів в процесах регулюється трьома важливими обмеженнями:

• сигнали не можуть декларуватись всередині процесів;

• будь-які присвоєння сигналам виконуються тільки після припинення процесу; до того часу всі

сигнали містять попередні значення;

• виконується тільки останнє присвоєння сигналу, вказане всередині процесу; отже немає сенсу

присвоювати сигналу більше одного значення всередині даного процесу.

Обмеження на використання сигналів має сильний вплив на їх практичне застосування.

Неможливість декларування сигналів всередині процесів – не головна проблема, але правила

присвоєння мають серьозні наслідки: оскільки сигнали можуть зберігати тільки останнє присвоєне

значення, вони не можуть використовуватись для збереження проміжних та тимчасових данних

всередині процесу. Інша важлива незручність полягає в тому, що нові значення присвоюються

сигналам не під час виконання присвоєння, а після припинення процесу. Це значно ускладнює

аналіз проекту.

Оскільки сигнали не можуть декларуватись всередині процесів і присвоєння ним значень

виконується після припинення процесу, необхідний об’єкт, який можна було би декларувати

всередині процесу, і який би забезпечував миттєве збереження тимчасових даних. Такий об’єкт у

VHDL називається змінною.

Декларування та присвоєння змінних

Змінні подібні сигналам. Однак є і деякі відмінності.

Змінні обмежені процесами, вони декларуються в процесах і не можуть використовуватись

поза ними. Декларація змінної виглядає аналогічно декларації сигналу. Єдина різниця полягає в

тому, що змінні декларуються з ключовим словом variable замість signal.

Присвоєння змінних виконується за допомогою символа ‘: =’. Це присвоєння виконується

миттєво і кожній змінній може бути присвоєно нове значення стільки разів, скільки потрібно.

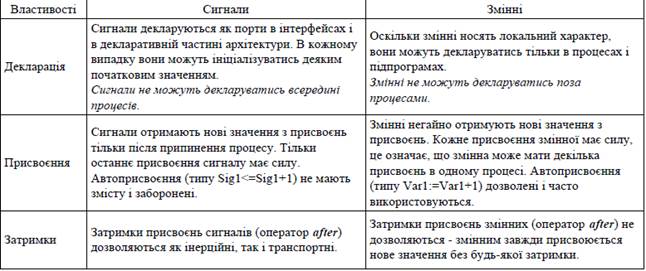

***тут мала бути ніхуйово здарова табличка на лист А4 дрібним шрифтом***

Порівняння сигналів і змінних

Кожний сигнал має три властивості: тип, значення і час. Є досить тісний зв’язок між

значенням і часом, оскільки для кожного сигналу відбувається його трасувальний запис в часі. Цей запис називається історією сигналу і дозволяє перевірити, які значення сигнал мав раніше, або в який момент відбулася його зміна.

З іншого боку, змінна має тільки дві властивості: тип і значення. Оскільки немає

відповідності між її значенням і часом, змінна може мати тільки біжуче значення.

Як вже згадувалось раніше, якщо сигнали і змінні мають однаковий тип, їх значення можуть

присвоюватись одне одному.

Керування послідовністю виконання операторів

Вступ

Процеси, в яких всі оператори виконуються послідовно зустрічаються дуже рідко. Оскільки

процеси представляють реальні системи, в яких постійно змінюються умови середовища, і їх

виконання звичайно відрізняються одне від одного.

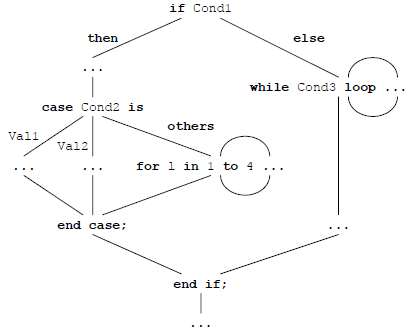

Зміна умов середовища представляється у VHDL чотирма класами умовних операторів:

• умовне виконання операторів (оператори if … then …),

• умовні виконання з альтернативою (оператори if … then … else … і if … then … elsif …),

• оператори вибору (оператор case …),

• цикли, що дозволяють повторювати виконання деяких операторів (оператори while … do … і

for … do …).

ExProc: process (SensitivityList)

begin

if Cond1

then

...

case Cond2 is

when Val1 =>...

when Val2 =>...

when others => for l in 1 to 4 loop

...

end loop;

end case;

else

while Cond3 loop

...

end loop;

...

end if;

...

end process ExProc;

ExProc: process (SensitivityList)

begin

end process ExProc;

Умовний оператор

Деякі оператори виконуються тільки коли виконуються вказані умови. Такі оператори

називаються умовними і їх реалізація описується як

if condition_met then execute_operations

Під виконанням VHDL-операції розуміють наступну процедуру:

• умова “condition_met” обчислюється як булевий вираз (true або false); якщо він істинний, то

активується підоператор “then”;

• після підоператора “then” знаходиться список операцій (операторів), що мають

виконуватись, кожний оператор закінчується крапкою з комою;

• для закінчення умовного оператора і для відокремлення його від наступних операторів

відразу після останнього оператора вказується підоператор “end if”.

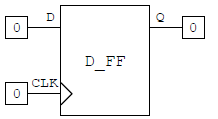

D_FF: process (D, CLK)

begin

if rising_edge(CLK)

then

Q < = D;

end if;

end process D_FF;

Умовний оператор з альтернативою

Описаний вище умовний оператор досить простий і вимагає деякого розширення для

підвищення гнучкості. Наприклад, необхідно описати такий випадок, як “якщо виконується умова,

виконати деякі дії, якщо ні – виконати інші дії”. Ця конструкція представляється оператором “if …

then … else …”.

Цей оператор розгалуження може бути розширений. Коли активний підоператор “else”, він

може містити інший умовний оператор, формуючи ієрархічну умову. Така ситуація підтримується

у VHDL конструкцією “if … then … elsif …”.

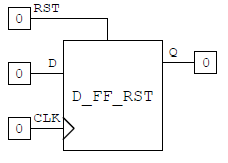

D_FF_RST: process (D, CLK, RST)

begin

if RST = '1'

then Q < = '0'

elsif rising_edge(CLK)

then

Q < = D;

end if;

end process D_FF_RST;

Множинний вибір

Конструкція “if … then … elsif …” – це оператор множинного вибору, який дозволяє

вибирати тільки одну гілку з декількох у відповідності з обчисленими умовами. Однак такі

конструкції швидко стають нечитабельними, якщо кількість гілок (вкладених “if”) перевищує три.

В такій ситуації краще використовувати оператор множинного вибору “case”.

Замість логічного виразу в операторі case описується вираз дискретного типу (довільний

перечислимий або цілий тип), або одномірний масив символів. На практиці в якості цього виразу

використовується ім’я об’єкту.

Кожна альтернативна група дій починається з підоператора “when choices => ”, де “choices”

визначається значенням виразу. Ці значення можуть бути одиничними значеннями, діапазонами

значень або альтернативами, але кожний з варіантів може зустрічатись лише один раз.

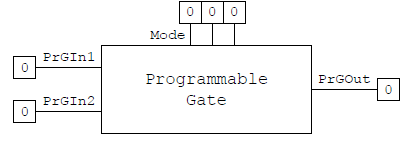

ProgrGate: process (Mode, PrGIn1, PrGIn2)

begin

case Mode is

when " 000" => PrGOut < = PrGIn1 and PrGIn2;

when " 001" => PrGOut < = PrGIn1 or PrGIn2;

when " 010" => PrGOut < = PrGIn1 nand PrGIn2;

when " 011" => PrGOut < = PrGIn1 nor PrGIn2;

when " 100" => PrGOut < = not PrGIn1;

when " 101" => PrGOut < = not PrGIn2;

when others => PrGOut < = '0';

end case;

end process ProgrGate;

Умовний цикл

Оператор умовного циклу починається з логічної умови і працює аналогічно умовному

оператору “if … then …”, але в ньому відбувається перехід на початок циклу після останнього

оператора. Цикл повторюється до тих пір, поки виконується умова на початку циклу. Спочатку

перевіряється умова, і, якщо вона істинна, виконуються оператори всередині циклу. Якщо ж умова

хибна, цикл вважається закінченим і керування передається першому оператору після циклу.

Як правило, такі цикли використовуються для повторення виконання набору операторів до

тих пір, поки сигнал або змінна відповідає вибраному критерію, наприклад певному значенню.

Наступний приклад – це лічильник, який підраховує додатні фронти сигналу CLK поки

сигнал Level рівний ‘1’. При цьому стабільність сигналу Level не аналізується. На початку циклу

тільки перевіряється рівність ‘1’ сигналу Level при визначенні додатнього фронту сигнала CLK. І

немає значення, чи змінювалось значення сигналу Level після останньої перевірки.

process

variable Count: integer: = 0;

begin

wait until CLK = '1';

while Level = '1' loop

Count: = Count +1;

wait until CLK = '0';

end loop;

end process;

Цикл з лічильником

Деколи може бути потрібно повторювати операції визначену кількість разів. Для цього

зручно використовувати цикл “for … loop …”.

Цикл for не містить явної логічної умови. Замість цього задається дискретний лічильник із

діапазоном значень і цикл повторюється доти, доки цей лічильник не вийде за межі діапазона.

Після кожної ітерації циклу, лічильнику присвоюється наступне значення із заданого діапазону.

Лічильник, який не потрібно декларувати (його специфікація в заголовку циклу прирівнюється до

декларування) всередині циклу вважається константою і може використовуватись в присвоєннях,

індексах виразів, але не може бути змінений. Більше того, лічильник існує тільки всередині циклу,

в якому він задекларований.

Діапазон лічильника не потрібно задавати в класичній формі вигляду from … to …. Він може

бути також заданий як підтип або перечислимий тип. В такому випадку тільки (під)тип задається в

якості діапазону лічильника.

***тут мала бути ніхуйово здарова табличка на лист А4 дрібним шрифтом***

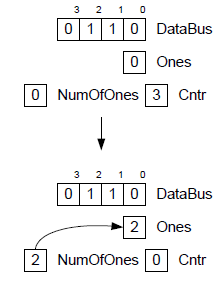

Переривання циклів

Цикли while і for повторюють виконання всіх своїх операторів до тих пір, поки виконується

умова циклу. Однак деколи буває необхідно пропустити деякі оператори циклу в біжучій ітерації і

перейти безпосередньо до наступної ітерації цього циклу. Така ситуація може виникнути,

наприклад, при підрахунку бітів, рівних ‘1’ у векторі бітів (наступний приклад): якщо біт рівний

‘1’ – лічильник збільшується на 1, якщо ж ‘0’ – цикл повинен перейти до наступної ітерації. Такий

тип операції забезпечується за допомогою оператора next.

signal DataBus: bit_vector(3 downto 0);

signal Ones: integer;

CountOnes: process (DataBus)

variable NumOfOnes: integer: = 0;

begin

for Cntr in 3 downto 0 loop

next when DataBus(Cntr) = '0';

NumOfOnes: = NumOfOnes + 1;

end loop;

Ones < = NumOfOnes;

end process CountOnes;

Крім оператора next, який виконує операцію переходу на наступну ітерацію, бувають

ситуації, яки вимагають припинення циклу, навіть якщо його умова істинна. В таких випадках

використовується оператор exit.

Для переходу на наступну ітерацію і виходу з циклу може бути задана умова виконання.

Оскільки такі операції використовуються дуже часто, у VHDL існує спрощений засіб для задання

умов операторів next і exit: ця умова задається в підоператорі when після вказаного оператора.

Оператор null

Оператор null не виконує ніяких дій і просто передає керування на наступний оператор. Він

може використовуватись для того, щоби вказати, що при певних умовах ніяких дій виконувати не

потрібно.

case OPCODE is

when " 001" => TmpData: = RegA and RegB;

when " 010" => TmpData: = RegA or RegB;

when " 100" => TmpData: = not RegA;

when others => null;

end case;

6. Множинні процеси у VHDL-архітектурі. Паралельність.

Оператори присвоєння сигналів як спрощені процеси.

Драйвери та атрибути сигналів. Багатозначна логіка.

Паралельність

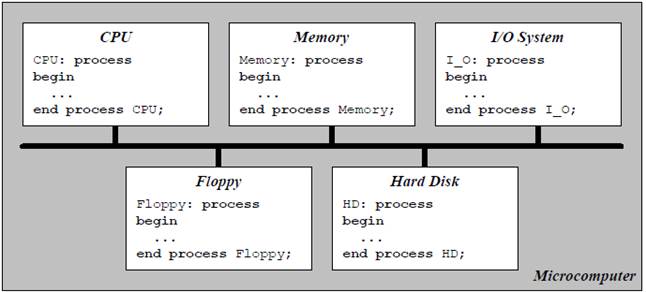

Паралельна природа систем

Хоча зручно описувати реальні процеси як послідовні, це дуже спрощенний підхід. Світ

взагалі не є послідовним. Всі реальні події відбуваються одночасно, тобто паралельно.

Деякі системи можуть складатись з паралельних підсистем. На відповідному рівні деталізації

поведінку окремої підсистеми можна описати як послідовність дій або процесів.

Оскільки VHDL – це ієрархічна мова, вона дозволяє описувати системи такими, якими вони є

реально – як набір паралельно працюючих підсистем. Кожна з таких взаємнопов’язаних систем

описується як окремий процес. Рівень деталізації залежить від потреби – один процес може

описувати поведінку складного компонента (наприклад, процесора), а інший – логічного вентиля.

Отже, поведінковий опис системи – це набір паралельних послідовних процесів.

Структура поведінкових архітектур

Подібно до інших складних конструкцій VHDL, архітектура складається з шаблона і тіла.

Шаблон описує, що це є архітектура, задає її ім’я і границі. Він також містить декларації

внутрішніх об’єктів архітектури. Тіло архітектури містить всі процеси архітектури.

Унікальною властивістю заголовку архітектури є асоціація її із інтерфейсом, оскільки кожна

архітектура має відноситись до певного інтерфейсу.

Тіло архітектури має паралельну структуру, яка деколи є досить важкою для розуміння,

оскільки всі оператори (процеси і їх вміст) записуються послідовно. Тим не менше, всі процеси в

будь-якій архітектурі виконуються паралельно.

Шаблон архітектури звичайно подібний на шаблон інтерфейса за виключенням того, що він має

додаткову частину “ім’я інтерфейсу”, яка відносить цю архітектуру до конкретного

інтерфейсу.

Декларація архітектури. Будь-які локальні (внутрішні) об’єкти архітектури описуються між

заголовком архітектури і ключовим словом begin. Ці об’єкти невидимі поза архітектурою.

Процеси. Всі процеси в архітектурі є паралельними між собою, тобто поновлені процеси

виконуються паралельно. В той же час всі оператори всередині процесів виконуються

послідовно.

Оператори всередині процесів. Хоча в загальному процеси виконуються паралельно, для

операторів кожного процесу забезпечується послідовний порядок виконання.

Виконання архітектури

Паралельне виконання процесів і послідовне виконання операторів всередині процесів є

дещо незвичним. Змішування послідовних та паралельних операцій є однією з найскладніших

концепцій VHDL.

Як вказувалось раніше, припинений процес поновлюється (активується), якщо змінюється

значення якогось з сигналів з його списку чутливості. Це правило дійсне і для множинних

процесів в архітектурі, і, коли змінюється значення сигналу, поновлюються всі процеси, в списки

чутливості яких входить цей сигнал. Оператори всередині поновлених процесів виконуються

послідовно. Але при цьому вони виконуються незалежно від інших процесів.

Ідею паралельності можна краще зрозуміти, якщо записати процеси не один під одним, а

рядом.

Передача інформації між процесами

Оскільки процеси не розрізняють сигнали, згенеровані ззовні (що надходять від середовища)

і згенеровані всередині (задекларовані всередині архітектури), сигнали, які активують процеси,

можуть бути згенеровані іншими процесами в тій самій архітектурі. Як тільки сигнал із списку

чутливості процесу змінює значення, процес активується. Це відбувається незалежно від того, був

сигнал змінений системним середовищем чи іншим процесом.

Інформація між процесами може передаватись тільки за допомогою сигналів. Оскільки

змінні є локальними об’єктами процесів, вони для цього непридатні.

architecture SomeArch of SomeEnt is

begin

P1: process (A, B, E)

begin

somestatement;

somestatement;

D < = someexpression;

end process P1;

P2: process (A, C)

begin

somestatement;

somestatement;

somestatement;

E < = someexpression;

end process P2;

P3: process (B, D)

begin

somestatement;

somestatement;

somestatement;

end process P3;

end architecture SomeArch;

Зміна A

1. Зміна значення сигналу A активує процеси P1 і P2. Послідовність операторів

всередині цих процесів буде виконана, після чого процеси припиняються. Останніми

операторами цих процесів є присвоєння сигналів D і E, які містяться в списках

чутливості процесів P3 і P1 відповідно.

2. Оскільки сигнали D і E змінили значення, процеси P3 і P1 активуються. Однак

якщо сигналу буде присвоєне теж саме значення, що він мав перед тим, він не

активує процес, чутливий до цього сигналу.

3. Сигналу D присвоюється деяке значення. Якщо це значення відрізняється від

попереднього, процес P3 знову поновлюється. Якщо ж ні - процес P3 не буде

активований.

Зміна B

1. Зміна значення сигналу B активує процеси P1 і P3. Послідовність операторів

всередині цих процесів буде виконана, після чого процеси припиняються. Останнім

оператором процесу P1 сигналу D, який є в списку чутливості процесу P3,

присвоюється деяке значення.

2. Сигналу D присвоюється деяке значення. Якщо це значення відрізняється від

попереднього, процес P3 знову поновлюється. Якщо ж ні - процес P3 не буде

активований.

Зміна C

1. Зміна значення сигналу C активує тільки процес P2. Послідовність операторів

всередині цього процесу буде виконана, після чого процес припиняється. Останнім

оператором цього процесу є присвоєння сигналу E, який міститься в списку

чутливості процесу P1.

2. Сигналу E присвоюється деяке значення. Якщо це значення відрізняється від

попереднього, процес P1 буде поновлений. Якщо ж ні - процес P1 не активується.

3. Якщо процес P1 був поновлений, в останньому його операторі виконується

присвоєння сигналу D, що міститься в списку чутливості процесу P3. Якщо це

значення відрізняється від попереднього, процес P3 поновлюється. Якщо ж ні -

процес P3 не буде активований.

Присвоєння сигналів як спрощені процеси

Прості процеси – присвоєння сигналів

Деколи буває необхідно використовувати прості логічні вентилі в якості окремих модулів

архітектури, наприклад:

OutAND < = InAND1 and InAND2;

Опис такої поведінки за допомогою процесу вимагає трьох додаткових операторів (заголовок

процесу, оператор begin і оператор end process), що є зайвим для наведеного вентиля AND. VHDL

дозволяє спростити такий однооператорний процес до одиничного рядка оператора присвоєння,

який називається паралельним присвоєнням сигналу.

Оператор паралельного присвоєння сигналу може з’являтися всередні архітектури

паралельно з іншими процесами і виконуватись паралельно з іншими присвоєннями, так само, як і

процеси. Однак, якщо вони представляються паралельними присвоєннями сигналів, то і

виконуються вони паралельно.

architecture SomeArch of SomeEnt is

signal Int1, Int2: bit;

begin

Gate1: process (A, C)

begin

Int1 < = A or C;

end process Gate1;

Gate2: process (B, D)

begin

Int2 < = B or D;

end process Gate2;

Gate3: process (Int1, Int2)

begin

Out < = Int1 and Int2;

end process Gate3;

end architecture SomeArch;

СТРІЛОЧКА ВНИЗ

architecture SomeArch of SomeEnt is

signal Int1, Int2: bit;

begin

Int1 < = A or C;

Int2 < = B or D;

Out < = Int1 and Int2;

end architecture SomeArch;

Активація паралельних присвоєнь

Процеси містять списки чутливості або оператор wait для визначення умови їх активації або

поновлення. Але паралельні оператори присвоєння не містять ніяких операторів wait або списків

чутливості.

Як показано в наступному прикладі, списки чутливості усіх процесів містять сигнали, які

з’являються пізніше у виразах, значення яких присвоюються вихідним сигналам процесів. Отже,

паралельні присвоєння сигналів є чутливими до зміни будь-якого сигналу, що знаходиться справа

від символу присвоєння. Фактично, саме так VHDL-симулятори і працюють: зміна будь-якого з

сигналів в правій частині паралельного присвоєння сигналу активує виконання цього присвоєння.

Таке присвоєння може бути затримане за допомогою оператора after як інерційною, так і

транспортною затримкою.

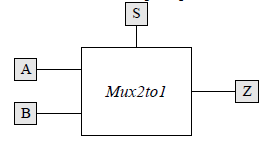

Умовне присвоєння сигналу

Деколи необхідно виконати присвоєння сигналу, якщо умова істинна. В зв’язку з тим, що

умовний оператор “if … then …” є послідовним оператором і може використовуватись лише в

процесах, необхідне умовне присвоєння сигналу, яке можна було би використовувати всередині

архітектури. Це функціональний еквівалент умовного оператора, але він записується інакше для

того, щоби їх можна було б розрізнити між собою.

Синтаксис умовного оператора присвоєння відповідає порядку, за яким він записується:

“присвоїти визначене значення сигналу, якщо виконується умова, а якщо ні (else) – присвоїти інше

значення”. Підоператор else може бути відсутнім.

Важлива різниця між умовним присвоєнням сигналу і умовним оператором полягає в тому,

що використання першого обмежено тільки присвоєннями сигналів, в той час як останній може

використовуватись для довільних послідовних операторів.

architecture Conditional of Mux2to1 is

begin

Z < = A when S = '1' else

B;

end architecture Conditional;

СТРІЛОЧКА ВНИЗ

architecture CondinProc of Mux2to1 is

begin

Mux: process (A, B, S)

begin

if S = '1'

then Z < = A;

else Z < = B;

end if;

end process Mux;

end architecture Conditional;

Присвоєння сигналу із вибором

Для умовного присвоєння сигналу одного з декількох значень використовується конструкція

присвоєння сигналу із вибором. Це паралельна конструкція, яка не може використовуватись

всередині процесів, де замість неї використовується оператор case, і навпаки, оператор case не

може використовуватись поза процесами, замість нього в такому випадку використовується

присвоєння сигналу із вибором.

Слід зауважити, що присвоєння сигналу із вибором, на відміну від оператора case, обмежено

тільки операторами присвоєння і не може містити інших операторів.

architecture SelBased of ProgrammableGate is

begin

with Mode select

PrGOut < =

PrGIn1 and PrGIn2 when " 000",

PrGIn1 or PrGIn2 when " 001",

PrGIn1 nand PrGIn2 when " 010",

PrGIn1 nor PrGIn2 when " 011",

not PrGIn1 when " 100",

not PrGIn2 when " 101",

'0' when others;

end architecture SelBased;

СТРІЛОЧКА ВНИЗ

architecture CaseBased of ProgrammableGate is

begin

ProgrGate: process (Mode, PrGIn1, PrGIn2)

begin

case Mode is

when " 000" => PrGOut < = PrGIn1 and PrGIn2;

when " 001" => PrGOut < = PrGIn1 or PrGIn2;

when " 010" => PrGOut < = PrGIn1 nand PrGIn2;

when " 011" => PrGOut < = PrGIn1 nor PrGIn2;

when " 100" => PrGOut < = not PrGIn1;

when " 101" => PrGOut < = not PrGIn2;

when others => PrGOut < = '0';

end case;

end process ProgrGate;

end architecture SelBased;

Драйвера і атрибути сигналів

Концепція драйвера

Присвоєння значення сигналу відбувається після припинення процесу. Більше того, якщо

сигналу присвоюється декілька значень на протязі виконання процесу, тільки останнє присвоєння

має силу. При цьому необхідно зберігати інформацію про події з сигналами.

Ця функція виконується драйвером. VHDL-компілятор створює драйвер для кожного

сигналу, якому присвоюється значення всередині процесу. Правило дуже просте: неважливо,

скільки значень присвоювалось сигналу – існує тільки один драйвер сигналу в процесі. Усі

операції виконуються із драйвером, значення з якого копіюється в сигнал тільки після припинення

процесу.

ExProc: process (SigA, SigB)

begin

SigC < = SigA;

...

SigC < = SigB + 1;

end process ExProc;

SigA = 0

SigB = 1

SigC = 0

ExProc_SigC = 0

--------------------------------

ExProc: process (SigA, SigB)

begin

SigC < = SigA;

...

SigC < = SigB + 1;

end process ExProc;

SigA = 1

SigC = 0

SigB = 1

ExProc_SigC = 0

Будь-яка яка зміна сигналу з списку чутливості

активує асоційований процес і драйвера всіх

сигналів, яким присвоюється нове значення -

по одному драйверу на сигнал.

--------------------------------

ExProc: process (SigA, SigB)

begin

SigC < = SigA;

...

SigC < = SigB + 1;

end process ExProc;

SigA = 1

SigC = 0

SigB = 1

ExProc_SigC = 1

Присвоєння виконується не безпосередньо

сигналу, а його драйверу. Значення драйвера

буде потім скопійоване в сигнал після

припинення процесу.

ExProc: process (SigA, SigB)

begin

SigC < = SigA;

...

SigC < = SigB + 1;

end process ExProc;

SigA = 1

SigC = 0

SigB = 1

ExProc_SigC = 2

Наступне присвоєння сигналу виконується над

драйвером, відміняючи попередньо збережену

інформацію. Ось чому тільки найостанніше

присвоєння сигналу має силу.

--------------------------------

ExProc: process (SigA, SigB)

begin

SigC < = SigA;

...

SigC < = SigB + 1;

end process ExProc;

SigA = 1

SigC = 2

SigB = 1

ExProc_SigC = 2

Коли процес припиняється, дані з драйверів

копіюються у відповідні сигнали. Ця операція

ще називається " фізичним присвоєнням

сигналу".

Історія і майбутнє сигналів

Завдяки драйверам сигнали можуть мати минулі, теперішні та майбутні значення. Драйвера

містять біжучі значення сигналів. Крім того, драйвера можуть також описувати проектовану

вихідну часову діаграму сигналу. Кожному драйверу може відповідати така часова діаграма, яка

складається з послідовності однієї або більше транзакцій. Транзакція складається із значення

сигналу і часу. Час описує момент, коли драйверу буде присвоєне нове значення, що описується

транзакцією.

Часова діаграма може бути описана явно як послідовність значень з асоційованими

затримками відносно однієї точки часу. Часові діаграми можна розглядати як проектоване

майбутнє сигналів. Оскільки симулятори зберігають транзакції для кожного сигналу, вони

створюють в результаті історію сигналів.

Часозалежні атрибути сигналів

Опис майбутнього сигналів важливий для створення тестових стендів, на яких VHDL-

описи тестуються у VHDL-середовищі, а стимулятори представляються часовими діаграмами.

Тестові стенди будуть розглянуті пізніше.

Історія сигналу потрібна з декількох причин. Наприклад, маючи тільки біжуче значення

сигналу, не можна перевірити, чи змінювався сигнал раніше, або перевірити його на зростаючий

чи спадаючий фронт. Історія сигналу представляється атрибутами сигналу. Атрибути – це

інформація про сигнал, яка автоматично оновлюється на основі історії сигналу. Ця інформація

включає попереднє значення сигналу, інтервал часу, який пройшов з моменту останньої зміни

значення сигналу, і т.п. Для отримання біжучого значення атрибуту потрібно задати ім’я сигналу,

за ним слідує апостроф і ім’я атрибута.

До часозалежних атрибутів відносяться наступні атрибути сигналів:

• S’transaction – має тип Boolean із значенням true, коли відбувається переприсвоєння

сигналу S;

• S’event – має тип Boolean із значенням true, коли відбулась зміна значення сигналу S;

• S’last_event – має тип time і визначає час, що пройшов від останньої події із сигналом S;

• S’last_value – попереднє значення, яке сигнал мав безпосередньо перед останньою зміною

сигналу S;

• S’stable(T) – має тип Boolean із значенням true, якщо сигнал S стабільний на протязі

останніх T одиниць часу.

Інші атрибути

Атрибути, що мають відношення до історії сигналів – не єдині доступні атрибути. Взагалі

атрибути дуже часто використовуються у VHDL і мова визначає 36 різних атрибутів для різних

класів об’єктів: скалярних типів, дискретних типів, масивів, сигналів та іменованих інтерфейсів.

Повний список визначених атрибутів можна знайти в Reference Guide.

Крім вже визначених атрибутів можна визначати власні атрибути, розширюючи VHDL-набір

майже необмежено.

Атрибути мають багато застосувань – від визначення фронту (на основі атрибуту ’event) до

незалежних від розміру описів. Деякі з найбільш типових прикладів застосування атрибутів

представлені в наступній таблиці.

Багатозначна логіка

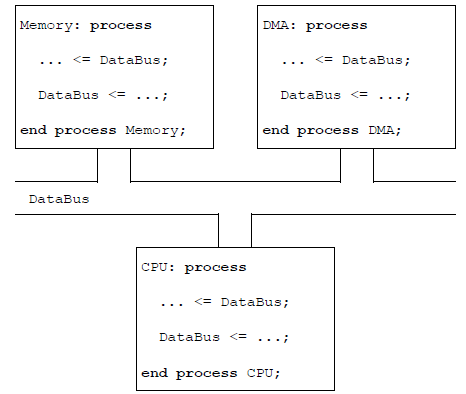

Багатодрайверні сигнали

Сигнали з декількома джерелами зустрічаються в багатьох реалізаціях. Наприклад,

комп’ютерна шина даних може отримувати дані від процесора, пам’яті, дисків та пристроїв вводу-

виводу. Кожний з цих пристроїв керує шиною і кожна сигнальна лінія шини може мати декілька

драйверів. Оскільки VHDL є мовою опису цифрових систем, такі багатодрайверні сигнали

природньо підтримуються у VHDL.

Важко завчасно визначити напевно, чи буде багатоджерельний сигнал керуватись завжди

тільки одним джерелом в один момент часу. В деяких системах це завжди буде так, в інших –

може бути навіть бажано змішувати сигнали від різних джерел, емулюючи, наприклад, операції

“монтажне І” або “монтажне АБО”. Взагалі, багатоджерельні сигнали вимагають встановлення

методу визначення результуючого значення у випадку, якщо декілька джерел паралельно видають

значення на одну і ту ж саму лінію.

VHDL-симулятор не може завчасно “знати” про те, чи буде багатодрайверний сигнал

активований двома або більше джерелами одночасно. Через це симулятор має бути готовим до

змішування значень сигналів. Таке “змішування” сигналів називається у VHDL розділенням.

Правила для змішування значень сигналів визначаються як таблиця, яка називається функцією

розділення. Таблиця будується з використанням усіх можливих значень сигналів по рядках і

стовбцях, і кожна її комірка містить інформацію про значення, яке буде згенероване, якщо два

відповідних значення будуть змішані.

Недоліки двозначної логіки

Розглянемо тип сигналу bit. Що станеться, якщо змішати ‘0’ і ’1’ (яке значення буде

отримане з ‘0’ і ’1’)? Проблема із типом bit полягає в тому, що неможливо визначити розділені

сигнали, використовуючи тільки два значення, і немає відповіді на вказане питання.

Цей факт має важливі наслідки: використовуючи тільки типи bit і bit_vector, неможливо

описати у VHDL мікропроцесор. Такі нерозділимі типи не можуть використовуватись для

багатодрайверних сигналів, які потрібні для опису шин даних (які обов’язково присутні у

мікропроцесорі). Для вирішення цієї проблеми необхідно використовувати деякі інші логічні типи

даних із більше ніж двома значеннями і функцією розділення, визначеною для всіх комбінацій

значень сигналів.

Багатозначна логіка

Одних тільки ‘0’ і ‘1’ недостатньо для розділення багатоджерельних сигналів. Навіть деякі

одноджерельні сигнали часто вимагають більше двох значень для представлення реальних

цифрових об’єктів:

• деколи неважливо, яке значення має сигнал – в цьому випадку використовується “довільне”

значення,

• буфери з трьома станами відключають драйвери від ліній сигналів в стані високого імпеданса,

це не є ‘0’ або ‘1’,

• деколи система може мати “неприсвоєні” або “невідомі” значення, які дещо відрізняються від

“довільних”.

Ці та декілька інших найбільш часто використаних значень описуються типом std_ulogic,

визначеним в пакеті Std_Logic_1164. Цей пакет містить також визначення векторного типу, що

базується на типі std_ulogic – std_ulogic_vector. Для обох типів визначений також набір базових

логічних операцій.

Символ ‘u’ в імені ulogic вказує на те, що це нерозділимі (unresolved) типи. Такі типи не

можуть використовуватись із багатодрайверними сигналами.

Роздільна багатозначна логіка

Тип std_ulogic підтримує всі значення, потрібні для опису типової цифрової системи. Однак

він є нерозділимим, що робить його непридатним у випадку багатодрайверних сигналів.

В зв’язку з цим в пакеті Std_logic_1164 визначений ще один тип: std_logic. Він об’єднує

потужність дев’ятизначної логіки std_ulogic із розділенням, надаючи VHDL-розробнику дійсно

універсальний логічний тип. Тип std_logic на сьогодні є промисловим стандартом де факто.

Єдина різниця між типами std_logic і std_ulogic полягає в тому, що перший є розділимою

версією останнього. Завдяки цьому всі операції і функції (в тому числі rising_edge і falling_edge),

визначені для std_ulogic, можуть використовуватись для std_logic без будь-яких додаткових

декларацій.

Існує також розділима версія для std_ulogic_vector, яка називається аналогічно:

std_logic_vector.

|

|