Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Порти мікроконтролера

|

|

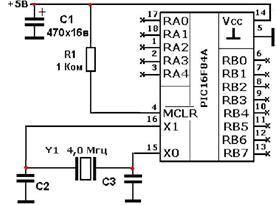

Мікроконтролери підгрупи PІС16F8X мають два порти: PORTA (5 біт) і PORTB (8 біт) з побітовим індивідуальним настроюванням на введення або на виведення.

Порт A (PORTA) являє собою 5-бітовий фіксатор, що відповідає виводам контролера RA< 4: 0>. Лінія RA4 має вхід тригера Шмдіта й вихід з відкритим стоком. Всі інші лінії порту мають ТТЛ вхідні рівні й КМОП вихідні буфери. Адреса регістра PORTA - 05h.

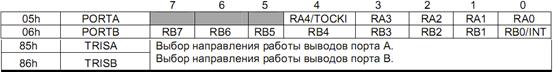

Рисунок 1 – Виводи портів

Кожній лінії порту поставлений у відповідність біт напрямку передачі даних, що зберігається в керуючому регістрі TRІSA, розташованому за адресою 85h. Якщо біт керуючого TRІSA регістра має значення 1, то відповідна лінія буде встановлюватися на введення. Нуль перемикає лінію на вивід і одночасно виводить на неї вміст відповідного регістра-фіксатора порту. При включенні живлення всі лінії порту за замовчуванням налаштовані на введення.

Операція читання порту А зчитує стан виводів порту, у той час як запис у нього змінює стан тригерів порту. Всі операції з портом є операціями типу " читання-модифікація-запис". Тому запис у порт припускає, що стан виводів порту спочатку зчитується, потім модифікується й записується в тригер-фіксатор.

Схема лінії RA4 порта А наведений на рисунку 2.

Порт В (PORTB) - це двонаправлений 8- бітовий порт, що відповідає виводам RB< 7: 0> контролера. Регістр прийом/передачі інформації PORTB розташований за адресою 06h. Стосовн порту В керуючий регістр TRІSB розташований на першій сторінці регістрів за адресою 86h. Якщо біт керуючого TRІSB регістра має значення 1, то відповідна лінія буде встановлюватися на введення. Нуль перемикає лінію на вивід і одночасно виводить на неї вміст відповідного регістра фіксатора. При включенні живлення всі лінії порту за замовчуванням налаштовані на введення

Рисунок 2 - Схема ліній RA < 3: 0 порту А. Рисунок 3 - Схема ліній RB < 7: 4 порти B.

У кожної ніжки порта В є невелике активне навантаження (близько 100мкА) на лінію живлення (pull-up). Вона автоматично відключається, якщо ця ніжка запрограмована як вивід. Більше того, керуючий біт /RBPU регістра OPTІON< 7> може відключити (при RBPU=1) всі навантаження. Скидання при включенні живлення також відключає всі навантаження.

Чотири лінії порта В (RB< 7: 4>) можуть викликати переривання при зміні значення сигналу на кожній з них. Якщо ці лінії настроєні на введення, то вони опитуються й фіксуються в циклі читання Q1. Нова величина вхідного сигналу порівнюється зі старою в кожному командному циклі. При розбіжності значення сигналу на ніжці й у фіксаторі генерується високий рівень.

Виходи детекторів " розбіжностей" RB4, RB5, RB6, RB7 поєднуються по АБО й генерують переривання RBІ (запам'ятовується в регістрі ІNTCON< 0>). Будь-яка лінія, налаштована як вивід, у цьому порівнянні не бере участь. Переривання може вивести кристал з режиму SLEEP.

При організації двонаправлених портів необхідно враховувати особливості організації введення/виведення даних МК. Будь-яка команда, що виконує її як " читання-модифікація-запис".

Наприклад, команди BCF і BSF зчитують порт цілком, модифікують один біт і виводять результат назад. Тут необхідна обережність. Зокрема, команда BSF PORTB, 5 (установити в одиницю біт 5 порту B) спочатку зчитує всі реальні значення сигналів, що є присутнім у цей момент на виводах порту. Потім виконуються дії над бітом 5, і нове значення байта цілком записується у вихідні фіксатори. Якщо інший біт регістра PORTB використовується в якості двонаправленного введення/виведення (скажемо, біт 0), і в цей момент він визначений як вхідний, то вхідний сигнал на цьому виводі буде зчитаний і записаний назад у вихідний тригер-фіксатор цього ж вивода, стираючи попередній стан. Доти, поки ця ніжка залишається в режимі введення, ніяких проблем не виникає. Однак якщо пізніше лінія 0 перемкнеться в режим виводу, її стан буде невизначеним.

На ніжку, що працює в режимі виводу, не повинні навантажуватися зовнішні джерела струмів (" монтажне І", " монтажне АБО"). Великі струми можуть ушкодити кристал.

Рисунок 4 - Регістри портів PORTA, PORTB та напрямки їх роботи

Примітка: напрямок роботи виводів портів А и В можна встановлювати в будь-яких комбінаціях.

Регістри TRISA і TRISB мають 5 і 8 робочих біти відповідно (по кількості виводів портів А и В). Їх адреси - 85h і 86h.

Біти регістрів TRISA і TRISB керують напрямком роботи виводів портів А та В. Якщо якийсь із цих бітів встановлюється в 1, то відповідний вивід порту працює " на вхід", тобто, приймає дані з виходу зовнішнього пристрою, підключеного до цього виводу.

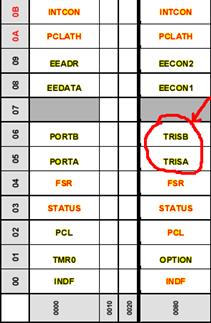

Рисунок 5 – Розміщення регістрів TRIS в області пам’яті даних

Якщо біт TRISA/TRISB встановлюється в 0, то відповідний вивід порту вже сам є джерелом сигналу для підключеного до цього виводу, входу зовнішнього пристрою, і програма може керувати цим зовнішнім пристроєм (наприклад, світлодіодом або якимось іншим виконавчим пристроєм).

За допомогою цих бітів, у межах кожного з портів, можна встановлювати різні комбінації напрямків роботи їхніх виводів, а також і міняти їх (напрямку) у ході виконання програми.

Через те, що регістри TRISA і TRISB перебувають в 1-му банку, то при роботі з ними, необхідно перейти в 1-й банк, зробити необхідні зміни бітів і повернутися в 0-й банк (якщо далі робота відбувається в нульовому банку). Для зміни банку необхідно скористатися регістром STATUS та його бітом RP0.

Регістри PORTA і PORTB керують фіксаторами портів А та В.

Кількість робочих бітів у них така ж, як і кількість виводів портів (5 і 8).

Фіксатор - це апаратно реалізований пристрій оперативної пам'яті, або тригер. Біти регістрів PORTA і PORTB керують цими тригерами. Якщо який-небудь із цих бітів встановити в 1, то на виході фіксатора (а значить і на відповідному виводі порту, настроєному " на вихід") також встановиться 1 (а для нуля - нуль).

Через те, що фіксатори є тригерами, то перехід їхніх виходів з одного стану в інший відбувається " одномоментно". Це означає те, що, наприклад, для виводу цифри на 7-сегментний індикатор, протягом певного програмного інтервалу часу, досить однієї команди на вивід цифри (байта) на початку цього інтервалу часу, і однієї команди на її скидання наприкінці цього інтервалу часу.

У проміжку часу між цими двома командами, програма може виконувати інші дії, формуючи за рахунок цих дій даний інтервал часу, причому ці дії можуть бути прямо не пов'язаними з роботою з виводу цифри в 7-сегментний індикатор.

Біти регістрів PORTA і PORTB фіксаторами керують завжди, але не завжди дані з виходів фіксаторів присутні на виводах портів. Виходи фіксаторів портів підключаються до виводів портів тільки при роботі цих виводів " на вихід".

При роботі виводів портів на вхід, виходи фіксаторів від відповідних виводів портів відключаються.

На відміну від виводів порту В, до яких можуть бути або підключені, або відключені внутрішні підтягуюючі резистори, виводи порту А внутрішньої " підтяжки" не мають. Таким чином, якщо вони налаштовані на роботу на вхід, то до них потрібно підключати зовнішні підтягуюючі резистори.

Приклад програми:

Виконання конфігурації розрядів 7 – 4 порту B на вивід, а розрядів 3 – 0 – на ввід інформації.

PORTB EQU 0x06; адреса регістру порту

; вводу/виводу

movlw b’00001111’

; | | | |

; | | | |└ ┴ ┴ ┴ ─ ─ ─ розряди 3-0 порту B на ввід

; └ ┴ ┴ ┴ ─ ─ ─ ─ ─ ─ ─ розряди 7-4 порту B на вивід

movwf TrisB; конфігурування порту B

…; продовження програми

Приклад програми.

Ввід інформації із порту A та запис її в комірку пам'яті даних з адресою 0x10.

…

PORTA EQU 0x05; адреса регістру порту вводу/виводу

MEM EQU 0x10; адреса регістру у пам'яті даних

movf PORTA, 0; ввід із порту A в регістр W

movwf MEM; запис в комірку пам'яті даних

…; продовження програми

|

|