Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Обобщённые алгоритмы управления технологическим циклом.

|

|

Сложные алгоритмы АСУТП, начиная с алгоритмов цифровых регуляторов параметров исполнительных устройств, опираются на типовые логические и арифметические процедуры, реализуемые процессорами управляющих микро-ЭВМ. Эти алгоритмы в конечном итоге воплощаются в УП, определяющие функционирование АСУТП. Порядок составления таких программ зависит от принятого языка программирования, но в любом случае в программе должны быть описаны все реализуемые ею арифметические и логические операции и даны точные указания относительно порядка их реализации, а также порядка поступления в УВМ входных и распределения выходных управляющих сигналов.

Предварительное описание действий УВМ по выполнению будущей УП может быть сделано обычным языком с применением соответствующей технической терминологии и условных обозначений. Однако подготовка программы значительно облегчится, если дополнительно составить алгоритм управления в виде особым образом подготовленной блок-схемы.

Основными графическими элементами схемы алгоритмов являются прямоугольники и ромбы. Прямоугольники служат для отображения арифметических операций и операций с запоминающими устройствами, а ромбы служат для задания логических условий. Графические элементы алгоритма располагают преимущественно сверху вниз в порядке выполнения действий, предусмотренных алгоритмом. Начало и конец алгоритма отмечают либо овалом, либо кружком. Затем графические элементы алгоритма соединяют стрелками, указывающими точную последовательность выполняемых операций и различные переходы, связанные с изменением порядка выполняемых операций.

В качестве примера рассмотрим составление алгоритма цифрового регулятора, действующего в замкнутом контуре управления электроприводом или другим исполнительным устройством (рис.5.20).

| Up(τ)=0, i=0 |

| i > m+1 |

| Ua = -am-i+1*Up(τ -i) |

| Up(τ) = Up(τ)+Ua |

| i > n |

| i > m+1 |

| Ub = bn-i*E(τ -i) |

| Up(τ) = Up(τ)+Ub |

| i = i+1 |

| II |

| Up(τ -1) = Up(τ); Up(τ -2) = Up(τ -1); …. E(τ -1) = E(τ); E(τ -2) = E(τ -1); …. |

| Up(τ) |

| Да |

| Да |

| Нет |

| Нет |

Рис.5.20. Алгоритм цифрового регулятора.

Общая формула разностного уравнения для вычисления регулирующего воздействия Up, формируемого регулятором в зависимости от величины рассогласования E на его входе, может быть представлена в следующем виде:

, (5.16)

, (5.16)

uде  – текущее дискретное значение регулирующего воздействия;

– текущее дискретное значение регулирующего воздействия;

– коэффициенты числителя той же функции;

– коэффициенты числителя той же функции;

– дискретное значение Е за i шагов квантования назад;

– дискретное значение Е за i шагов квантования назад;

– коэффициенты знаменателя дискретной передаточной функции регулятора;

– коэффициенты знаменателя дискретной передаточной функции регулятора;

– фиктивный коэффициент, введённый для упрощения программы;

– фиктивный коэффициент, введённый для упрощения программы;

– дискретное значение U за i шагов квантования назад.

– дискретное значение U за i шагов квантования назад.

Все коэффициенты ai и bi являются функциями периода дискретности Т, который обычно является параметром заданной цифровой системы управления.

Число шагов квантования за время t работы регулятора определяют по формуле:

, (5.17)

, (5.17)

где Т – такт, период дискретности цифровой системы управления (шаг квантования по времени).

Чтобы рассчитать текущее значение Up(τ), необходимо, судя по формуле (5.16), предварительно рассчитать все произведения вида bn-i*E(τ -i) и вида am-i+1*Up(τ -i), а затем их алгебраически сложить. Если расчёт начинается с момента времени τ = 0, то должны быть заданы все начальные значения величин Up(τ -i) и E(τ -i) и, конечно, все коэффициенты ai и bi. Задание этих величин в алгоритме, приведённом на рис.5.20, не показано, но оно подразумевается. Начало расчёта помечено на рис.5.20 цифрой 1, а конец расчёта – цифрой II (обе цифры – в кружках).

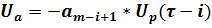

Расчёт начинается с задания нового дискретного значения E(τ) задающей частью системы управления, которой принадлежит данный регулятор. Поскольку все начальные условия расчёта Up(τ) учтены в формуле (5.16), то перед началом расчёта прошлое значение Up(τ) полагается равным нулю.: Up(τ) = 0. Обнуляется и переменная цикла расчётов (i = 0). Это означает, что обнуляются ячейки ОЗУ, в которых хранятся текущее значение Up(τ) и текущее значение переменной цикла. Первый сверху прямоугольник рассматриваемого алгоритма является, таким образом, заданием операций с ОЗУ. Далее в алгоритме (см. рис.5.20) организовано формирование m + 2 произведений типа:

,

,

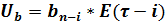

Включая фиктивное –am+1*Up(τ) при i = 0, которое является первым в цикле расчётов. Последнее произведение будет соответствовать i = m+1 и даст –a0*Up(τ -m-1). Дальнейшие расчёты произведений данного типа будут прекращены согласно условию, записанному в верхнем ромбе: i > m+1. Если это условие соблюдается (вариант «Да»), то совершается переход к расчёту произведений типа:

,

,

в обход расчёта произведений первого типа. Такой переход называется условным переходом (переход в обход некоторой части программы в случае выполнения заданного условия). Расчёт n+1 произведений второго типа ограничен условием i > n, т.е. совершается до тех пор, пока имеет место i ≤ n. После каждого из расчётов заданных произведений полученное произведение суммируется в состав Up(τ) по формуле:

,

,

или по формуле:

.

.

Это означает, что каждый раз из ОЗУ извлекается накопленное значение Up(τ) и к нему прибавляется либо Ua, либо Ub, пока не будут рассчитаны и суммированы в состав Up(τ) все заданные произведения. Если все произведения Ub подсчитаны, то по условию i > n (вариант «Да») происходит переход к проверке, все ли расчёты Ua выполнены, через исполнение условия i > m + 1. Это необходимо в тех случаях, когда имеет место m + 1 > n. В таких случаях, хотя расчёты по условию i > n будут завершены, условие i > m + 1 ещё не будет выполняться, так что расчёты Ua нужно будет продолжить. Для продолжения расчётов значение i увеличивается на единицу блоком i = i + 1.

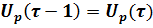

Одновременное выполнение условий i > n и i > m + 1 (вариант «Да») свидетельствует об окончании расчётов текущего значения Up, которое поступает на выход II (в кружке) и далее в систему управления силовой частью исполнительного устройства. В следующем такте Т, после поступления нового значения рассогласования Ep(τ), начнётся расчёт нового значения Up, а только что рассчитанное значение Up станет прошлым, что выражается соотношением:

.

.

Данная формула означает, что как только будет рассчитано значение Up(τ), оно будет занесено в ячейку ОЗУ, где до того хранилось значение Up(τ -1), т.е. предыдущее значение Up. Предварительно значение Up(τ -1) переносится в ячейку ОЗУ, где хранилось значение Up(τ -2), и т.д. Этот процесс называется сдвигом значений выходной величины. Аналогично производится сдвиг входной величины Е. Он продолжается до тех пор, пока не получит новое значение наименьшая по номеру из величин Up(τ) или Еp(τ). Данные сдвиги отображены в самом нижнем прямоугольнике схемы алгоритма (рис.5.20).

Время такта Т обычно является жёстко заданным (например, конструкцией исполнительного устройства) периодом дискретности, так что время выполнения расчётов величины Up(τ) должно (с некоторым запасом) укладываться во время Т. Следовательно, возможны различные подходы к разработке алгоритма и управляющей программы регулятора. Если время расчётов достаточно мало, то алгоритм и программу можно разбивать исходя из условия её минимальной длины (что и делалось), чтобы она занимала меньше места в ПЗУ. Если же время расчётов угрожающе велико, то программу разрабатывают исходя из требования обеспечения её максимального быстродействия.

При рассмотрении системы автоматизации в целом обсуждать подробности алгоритмов отдельных регуляторов, входящих в её состав, не представляется возможным. Схема общего алгоритма сложной системы обычно состоит из ряда прямоугольников, в которых размещаются названия разделов УП, и связывающих их ромбов основных логических условий функционирования системы. Такие алгоритмы необходимы как сжатое и удобное для обозрения описание системы автоматизации.

В качестве примера рассмотрим общий алгоритм микропроцессорной системы управления лифтом (рис.5.21).

| Да |

| Да |

| Начало |

| 1. Включение в работу |

| 2. Цепь безопасности разомкнута? |

| 3. Аварийная остановка |

| Да |

| Нет |

| 4. Необходим режим деблокирования? |

| 5. Подпрограмма режима деблокирования |

| 6. Поиск и устранение неисправности |

| 7. Управление из машинного отделения? |

| 10. Подпрограмма режима управления из машинного отделения |

| Нет |

| Нет |

| 8. Режим ревизии? |

| Да |

| 11. Подпрограмма режима ревизии |

| Нет |

| 9. Режим нормальной работы? |

| 11. Подпрограмма режима нормальной работы |

| Да |

| Нет |

| 13. Останов лифта |

| Конец |

Рис.5.21. Общий алгоритм микропроцессорной системы управления лифтом.

Функционирование системы управления в общих чертах становится понятным по надписям на схеме алгоритма. После включения в работу (блок 1 алгоритма) и в течение всего времени работы производится постоянный контроль цепи безопасности (ромб условного перехода 2). При размыкании этой цепи (вариант «Да») происходит аварийная остановка лифта (блок 3). Если кабина лифта остановилась на ловителях или от воздействия на конечные выключатели, то необходимо воспользоваться режимом деблокировки. В случае остановки по причине неисправности другого типа поиск и устранение неисправностей (блок 6) производится без вхождения в режим деблокировки.

Ромбы 7, 8 и 9 определяют условия задания тех или иных режимов управления лифтом, реализуемых программными блоками 10, 11 и 12. При этом в режиме ревизии шахты лифта управление лифтом возможно только с поста ревизии на крыше кабины. Выполнение программы управления лифтом согласно алгоритму, представленному на рис.5.21, продолжается до тех пор, пока не поступит команда остановки.

Для более подробного ознакомления с системой управления лифтом необходимо рассмотреть алгоритмы подпрограмм, входящих в состав общего алгоритма. Тогда окажется, что в них входят, в частности, алгоритмы управления режимами работы электропривода лифтового подъёмника. И только при рассмотрении составов последних алгоритмов дело дойдёт до рассмотрения алгоритмов функционирования регуляторов скорости и положения в составе цифровой системы управления электроприводом механизма подъёма, аналогичных рассмотренному ранее цифровому регулятору. В завершение должна быть рассмотрена реализация заданных алгоритмов управления средствами микропроцессорной техники.

При реализации заданных алгоритмов их иерархии приводится в соответствие иерархия управляющих микропроцессорных устройств, внутри которых с помощью системы приоритетов строится иерархия управляющих программ.

Приложение 5

Символы и функции стандартного кода ISO-7 для СПУ (ГОСТ 20999-83)

|

|