Главная страница

Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

|

Триггеры.

Простейшей триггерной ячейкой является асинхронный RS-триггер. Это ячейка с двумя входами (R и S) и двумя выходами: прямым выходом Q и инверсным выходом Ǭ. По сигналу S = 1 (Set – установка) RS -триггер устанавливается в единичное состояние, которому соответствует Q = 1 и Ǭ = 0. По сигналу R = 1 (Reset – сброс) RS -триггер сбрасывается в нулевое состояние, которому соответствует Q = 0 и Ǭ = 1. Когда на одном из входов RS -триггера имеется единичный сигнал, то на другой вход должен быть подан нулевой сигнал.

Одновременная подача единичных сигналов на оба входа RS -триггера не допускается.

При наличии на обоих входах RS -триггера нулевых сигналов его состояние не изменяется. Таким образом, RS -триггер является последовательностной управляющей ячейкой, характеризующейся двумя различными внутренними состояниями, каждое из которых целесообразно обозначать сигналом на прямом выходе: Q = 1 и Ǭ = 0. В такую ячейку можно записать и в ней хранить информацию, объём которой не превышает 1 бит (см. вопрос 2.2). Триггер – это стандартна ячейка ОЗУ для хранения информации ёмкостью 1 бит.

Функционирование RS -триггера может быть отображено таблицей выходов (табл.5.9).

Таблица 5.9

| Rt

| St

| Qt-1

| Qt

| Ǭ t

| Режим

| |

|

|

|

|

| Хранение информации Qt = Qt-1

| |

|

|

|

|

| |

|

|

|

|

| Запись 1 Qt = 1

| |

|

|

|

|

| |

|

|

|

|

| Запись 0 Qt = 0

| |

|

|

|

|

| |

|

|

| *(1)

| *(1)

| Запретная комбинация Ǭ t = Qt

| |

|

|

| *(1)

| *(1)

| Из табл.5.9 видно, что при R = 0 и S = 0 RS -триггер сохраняет своё состояние неизменным, т.е. хранит ранее записанную информацию: либо Q = 0, либо Q = 1. При подаче сигнала St = 1 на выходе устанавливается Qt = 1 вместо Qt-1 = 0 или сохраняется Q = 1. Аналогично при подаче Rt = 1 на выходе устанавливается Qt = 0.

Запретность комбинации R = 1 и S = 1 (одновременно) означает, что клетки со звёздочками можно заполнять произвольно, так как при нормальной эксплуатации RS -триггера одновременное поступление R = 1 и S = 1 исключено. При реализации RS -триггера на элементах ИЛИ-НЕ наиболее простая схема получается, если вместо звёздочек поставить нули, а при реализации на элементах И-НЕ из тех же соображений лучше поставить вместо всех звёздочек единицы, что и сделано. Составляя по табл.5.9 логические формулы (см. вопрос 5.2) для функций Qt и Ǭ t, получим следующие выражения:

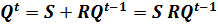

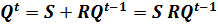

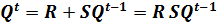

; (5.9) ; (5.9)

. (5.10) . (5.10)

Вторые части формул (5.9) и (5.10) позволяют непосредственно по ним получить схему RS -триггера на элементах И-НЕ, приведённую на рис.5.10.

Действительно, на выходе Ǭ t имеем:

, ,

а на выходе Qt соответственно получим:

, ,

что соответствует выражению (5.9).

Аналогично проверяется правильность выражения (5.10) относительно выхода Ǭ t схемы, показанной на рис.5.10.

Если в формуле (5.9) принять Q = H, S = dНdВ, а R = dВ, то она становится эквивалентной формуле (5.8). Таким образом, если на входе RS -триггера по схеме, представленной на рис.5.10, поместить элемент И-НЕ, дающий S = dНdВ, а на вход R подать сигнал dВ, то функции схем, представленных на рис.5.9, б и 5.10, совпадут.

Следовательно, схему регулирования уровня по формуле (5.8) можно строить на логическом элементе, реализующем функции RS -триггера, с добавлением элемента И-НЕ для реализации дополнительной логики по входу S. Условие недопущения одновременной подачи сигналов R = 1 и S = 1 здесь строго соблюдается.

Чтобы получить синхронный RS -триггер, нужно на его входах предусмотреть две ячейки И-НЕ, на которые подаётся синхронизирующий импульс С (рис.5.11).

Рис.5.10. Схема RS -триггера Рис.5.11. Синхронный RS -триггер:

на элементах И-НЕ а) – схема на элементах И-НЕ; б) – условное обозначение

Синхронный триггер переключается только при одновременной подаче единичных сигналов на один из информационных входов и на вход C (Clock). Так, при C = 1 и S = 1 имеем CS = 0 и триггер переключается в состояние Q = 1, Q = 0 или остаётся в этом состоянии (см. табл.5.9).

Путём подачи внутреннего сигнала CS на вход R синхронный RS -триггер превращается в триггер задержки – D -триггер (Delay – задержка).

У D -триггера вход R является внутренним, а информационный вход S переименован в D.

Состояние D -триггера принимает то значение, которое имеется на входе D: при D = 1 получим Q = 1, при D = 0 получим Q = 0, но только при условии, что C = 1. При С = 0 состояние выходов D -триггера не изменяется. Это свойство D -триггера можно использовать для организации считывания информации со входов управляющего устройства. Например, можно установить D -триггеры на входе преобразователя кода (см. рис.5.7, а) вместо элементов И-НЕ и подать входные сигналы на D -входы триггеров (рис.5.12). На их выходах будут получены как прямые, так и инверсные значения входных сигналов, какими они были в момент считывания информации с датчика положения, т.е. при сигнале синхронизации C2 = 1. Здесь совокупность D -триггеров играет роль регистра, в котором при C2 = 0 хранится записанная с датчиков при C2 = 1 информация.

| Рис.5.12. Синхронизация

поступления входных

сигналов X1, …, X4

| | Если во время обработки информации управляющим устройством сигнал C1 (см. рис.5.7, б) равен единицу, а сигнал C2 равен нулю, то обеспечивается стабильность получаемой от D-триггеров информации. Во время считывания входной информации C1 = 0, а C2 = 1. Обработка считываемой информации в это время не производится. После того как сигнал C2 становится равным нулю, даётся небольшая выдержка времени на завершение переходных процессов в преобразователе кода, когда сигнал C1 также равен нулю. Благодаря этому в период обработки считанной информации (при C1 = 1) информация на выходе преобразователя кода остаётся неизменной, эффект гонки импульсов полностью устраняется.

При синхронизации работы входных преобразователей управляющее устройство обеспечивает им работу в трёх состояниях:

1) считывание поступившей на его входы информации (C1 = 0, C2 = 1);

2) преобразование поступившей информации входным преобразователем (C1 = 0, C2 = 0);

3) хранение поступившей информации (C1 = 1, C2 = 0).

|

В результате при работе в синхронном режиме входной преобразователь приобретает черты устройства последовательностного действия. Например, преобразователь кода, схема которого представлена на рис.5.7, оказался снабжённым собственным запоминающим устройством в виде комплекта D -триггеров (см. рис.5.12).

Из других триггеров для нас представляют интерес счётный триггер (Т -триггер) и JK -триггер (рис.5.13). Т -триггеры лежат в основе схем различных счётчиков, а JK -триггеры являются универсальными в том смысле, что могут выполнять функции триггеров многих других типов. У Т -триггера имеется только один информационный (счётный) вход Т, который совпадает с тактовым входом С. После прохождения единичного импульса на счётном входе Т состояние триггера изменяется на противоположное.

Рис.5.13. Схема (а) и условные обозначения Т-триггера (б) и JK-триггера (в).

Поскольку входные импульсы (такты) могут быть различной длительности, Т -триггер должен запоминать не только то состояние (либо Qt = 1, либо Qt = 0), в котором он должен оказаться по окончании текущего такта, но и предыдущее состояние (либо Qt-1 = 0, либо Qt-1 = 1), на всё время подачи сигнала Т = 1. Иначе вновь сформировавшееся состояние будет восприниматься триггерной структурой (при условии сохранения Т = 1) как старое, что вызовет новое – лишнее – переключение (табл.5.10), за ним следующее, и так до тех пор, пока сохраняется Т = 1. Таким образом, необходимо запоминать старое значение Q на всё время, пока имеет место Т = 1, чтобы избежать автоколебаний. Для этого схема Т -триггера должна содержать две ячейки памяти, а не одну, как это было у рассмотренных выше RS - и D -триггеров.

Функционирование Т -триггера моделирует счёт в двоичной системе счисления. Действительно, при подаче единичного импульса на его вход (Т = 1) при условии, что значение выхода в этот момент времени равно нулю (Q = 0), значение выхода становится равным единице (Q = 1). Это соответствует добавлению единицы в какой-либо разряд двоичного числа, значение которого до того было равно нулю. При подаче следующего единичного импульса (Т = 1) значение выхода триггера изменится от Q = 1 к Q = 0. То же самое происходит при прибавлении единицы в какой-либо разряд двоичного числа, если его значение до того было равно единице. Однако в двоичном числе при этом произойдёт перенос единицы в следующий, старший разряд. Такой же перенос единицы произойдёт и на выходе счётного триггера, если к нему подключить вход следующего счётного триггера, как это делается в счётчиках (см. вопрос 5.6.3).

Универсальность JK -триггера заключается в том, что при подаче входных сигналов J = 1 или К = 1 раздельно он работает, как RS -триггер. Если же на вход К подавать инвертированный сигнал с входа J, то получится D -триггер. А при подаче J = K = 1 одновременно он работает как Т -триггер, т.е. изменяет своё состояние на противоположное после каждого прохождения единичного импульса на тактовом входе С. Следовательно, структура JK -триггера должна быть такой же, как Т-триггера, но должны быть предусмотрены отдельные информационные входы J и K. Этим требованиям удовлетворяет схема, приведённая на рис.5.13, а, которой соответствует (при J = K = 1) следующая таблица выходов (табл.5.11).

| Таблица 5.10

|

| Таблица 5.11

| | Tt

| Qt-1

| Qt

|

| Tt

| Qt-1

| Qt

| Qt+1

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

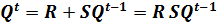

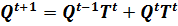

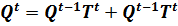

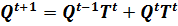

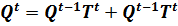

| Согласно табл.5.11 при Т = 1 изменяются только значения промежуточных выходов Qt, а значения основных выходов Qt+1 остаются неизменными (Qt+1 = Qt-1). При Т = 0 основные выходы принимают значение промежуточных: Qt=1 = Qt, а значения Qt при этом остаются неизменными. Функционирование основных выходов Т -триггера описывается формулой:

, (5.11) , (5.11)

полученной из таблицы выходов (5.11). Функционирование промежуточных выходов Т -триггеров соответствует таблице переходов (5.10) и описывается формулой:

. (5.12) . (5.12)

Автоколебаний в схеме, представленной на рис.5.13, а, не возникает, так как сигналы Qt-1 поступают не с выходов Qt, а с выходов Qt+1. При переключении триггера Qt (при Т = 1) состояние триггера Qt+1 не изменяется, так как его входные цепи запёрты блокировочными сигналами, поступающими либо с элемента D1, либо с элемента D2 на элементы D5 и D6.

Схема, представленная на рис.5.13, а, имеющая в своём составе две последовательно соединённых триггера, называемых двухступенчатым триггером. Двухступенчатость триггера обозначается на схемах знаком ТТ (см. рис.5.13, б, в).

|

; (5.9)

; (5.9) . (5.10)

. (5.10) ,

, ,

, , (5.11)

, (5.11) . (5.12)

. (5.12)