Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Адресация памяти. Управление памятью в защищенном режиме работы процессора.

|

|

Организация и адресация памяти в защищенном режиме:

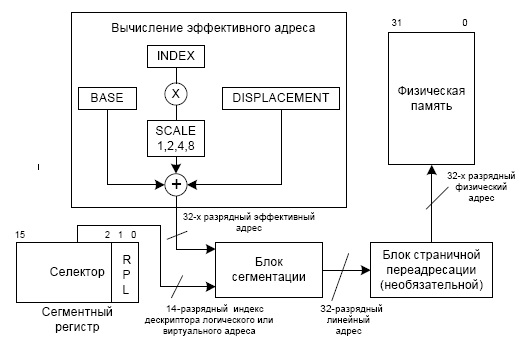

В защищенном режиме, также как и в реальном, существуют понятия логического и

физического адреса. Кроме сегментации в защищенном режиме возможно разбиение

(Paging) логической памяти на страницы размером 4 Кбайт, каждая из которых может

отображаться на любую область физической памяти. Начиная с 5-го поколения, появилась

возможность увеличения размера страницы до 4 Мбайт. Сегментация и разбиение на

страницы могут применяться в любых сочетаниях. Сегментация является средством

организации логической памяти на прикладном уровне. Разбиение на страницы

применяется на системном уровне для управления физической памятью. Сегменты и

страницы могут выгружаться из физичес-кой оперативной памяти на диск и по мере

необходимости подкачиваться с него обратно в физическую память. Таким образом

реализуется виртуальная память.

Применительно к памяти различают три адресных пространства: логическое, линейное и

физическое.

Основным режимом работы 32-разрядных процессоров считается защищенный режим,

в котором работают все механизмы преобразования адресных пространств.

Логический адрес (или виртуальных адрес) состоит из селектора сегмента и эффективного

адреса (смещения), обозначается seg: offset.

Преобразование логического адреса в физический выполняется не простым сложением со

сдвигом, а при помощи специальных таблиц преобразования адресов (специальной

области памяти). В первом приближении можно считать, что селектор для процессора

i80286 является индексом в таблице, содержащей базовые 32 разрядные адреса сегментов

(и не только). В процессе преобразования логического адреса в линейный процессор

|

прибавляет к базовому 32-разрядному адресу 32-разрядное смещение, т.е. линейный адрес

образуется сложением базового адреса сегмента с эффективным адресом.

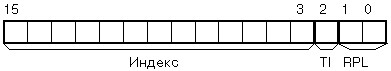

Из чего состоит селектор: не все 16 бит селектора используются для индексации по

таблице адресов. В качестве индекса выступают старшие 13 бит. Два младших бита (бит 0

и бит 1) используются системой защиты памяти. Бит 2 позволяет выбирать для

преобразования адреса один из двух типов преобразования адресов.

Поле TI (Table Indicator) состоит из одного бита. Если этот бит равен нулю, для

преобразования адреса используется так называемая глобальная таблица дескрипторов

GDT (Global Descriptor Table), в противном случае — локальная таблица дескрипторов

LDT (Local Descriptor Table).

Таблица дескрипторов — это просто таблица преобразования адресов, содержащая

базовые адреса сегментов и некоторую другую информацию. То есть каждый элемент

таблицы дескрипторов (дескриптор) содержит базовый адрес сегмента и другую

информацию, описывающую сегмент.

Таблица GDT — единственная в системе. Обычно в ней находятся описания сегментов

операционной системы. Таблиц LDT может быть много. Эти таблицы содержат описания

сегментов программ, работающих под управлением операционной системы, т.е.

отдельных задач. В каждый данный момент времени процессор может использовать

только одну таблицу LDT.

Эффективный адрес формируется сложением компонентов base, index, displacement с

учетом масштаба scale.

32-битный физический адрес памяти образуется после преобразования линейного адреса

блоком станичной переадресации. В простейшем случае при отключенном блоке

страничной переадресации физический адрес совпадает с линейным. Включенный блок

станичной переадресации осуществляет трансляцию линейного адреса в физический

страницами размеров 4 Кбайт (для последних поколений процессоров возможны станицы

размером 2-4 Mбайт). Блок обеспечивает и расширение разрядности физического адреса

процессоров шестого поколения до 36 бит. Блок переадресации может включаться только

в защищенном режиме.

Для обращения к памяти процессор совместно с внешними схемами формирует внешние

сигналы для операций записи и чтения. Шина адреса разрядностью 32-36 бит позволяет

адресовать 4/64 Гбайт физической памяти, но в реальном режиме доступен только 1

Мбайт, начинающийся с младших адресов.

|

Одноранговые и многоранговые сети.

Одноранговые сети состоят из компьютеров одного ранга, то есть все компьютеры в

сети занимают одинаковое положение. Такие сети не нуждаются в специальном

программном обеспечении.

В системах Windows 95 и старше есть все необходимое для управления одноранговой

локальной сетью. На рабочем столе есть значок Сетевое окружение, который открывает

окно, аналогичное окну Мой компьютер.

Многоранговые сети имеют два и более ранга. Если сеть двухранговая, то

компьютеры в сети организованы по следующему принципу: имеется одна центральная

машина, которая называется файл-сервером, и множество подключенных к ней

компьютеров – рабочих станций. Центральная машина имеет большую дисковую

память. В ней в виде файлов хранится программное обеспечение и другая информация,

к которой могут обращаться пользователи сети. Сеть носит название «клиент-сервер».

Название «сервер» происходит от английского server и переводится как

«обслуживающее устройство».

|

|