Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Короткі теоретичні відомості. Дослідження регістрів

|

|

Дослідження регістрів

Мета роботи: Ознайомлення з принципами побудови регістрів та їх експериментальне дослідження в пакеті Electronics Workbench v5.12.

Короткі теоретичні відомості

Регістром називається операційний вузол, що служить для запам'ятовування слів і забезпечуючий в загальному випадку виконання наступних мікрооперацій:

- встановлення регістра в нуль (скидання, гасіння);

- прийом слова з іншого регістра, лічильника і т.п.;

- передача слова на інший регістр, лічильника і т.п.;

- перетворення кодів збережених слів в інверсні коди;

- зсув слова вліво та вправо на необхідне число розрядів;

- перетворення послідовного коду в паралельний та навпаки;

Схеми конкретних регістрів в окремих випадках можуть реалізовувати лише деякі з перерахованих мікрооперацій. Звичайно регістри будують на тригерах RS, JK, DV, D або на Т - тригерах, які в свою чергу реалізовують мікрооперацію запам’ятовування слів.

Решта мікро операцій виконується за рахунок підключення до входів і виходів тригерів логічних елементів, а також за рахунок організації відповідних зв'язків між ними.

Паралельним регістром називається такий регістр, який реалізує всі перераховані мікрооперації, за винятком зсуву і перетворення послідовного коду в паралельний і навпаки.

Якщо в паралельному регістрі на вхід кожного каскаду інформація поступає по двох каналах в парафазному коді, то такий регістр називають парафазним. При існуванні тільки одного каналу (прямого або інверсного) надходження інформації в кожному розряді, регістр називають однофазним.

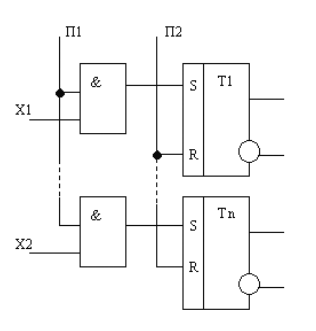

Схема паралельного однофазного регістра, що виконує мікрооперації встановлення регістра в нуль та прийом слова з іншого регістра, показана на рисунку 1.

Рис. 1 - Схема паралельного однофазного регістра

На нульові входи всіх тригерів подається сигнал установки нульового стану П0.

Після подачі цього сигналу всі тригери регістра будуть знаходитись в нульовому стані до появи на вхідних шинах записуючого слова і сигналу прийому П1.

В тих розрядах, де Хi=1, здійсниться установка тригерів в одиничний стан. Там де Хi=0, стани тригерів не зміняться.

Видача інформації з регістра може проводиться в прямому, інверсному та парафазному кодах.

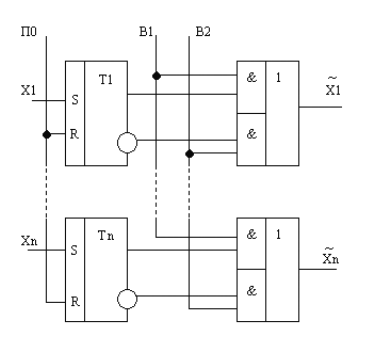

Схема видачі інформації в прямому та інверсному кодах показана на рисунку 2,

Рис. 2 - Схема видачі інформації в прямому та інверсному кодах

де:

В1 - сигнал видачі прямого коду;

В2 - сигнал видачі інверсного коду.

Одночасна поява сигналів В1 і В2 заборонена.

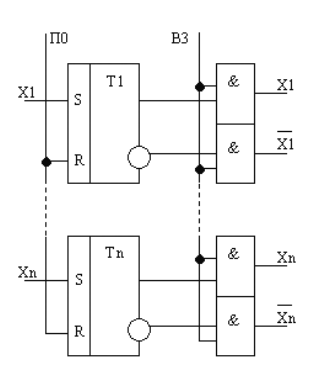

Схема регістра з видачею парафазного коду приведена на рисунку 3.

Рис. 3 - Схема видачі інформації в парафазному коді

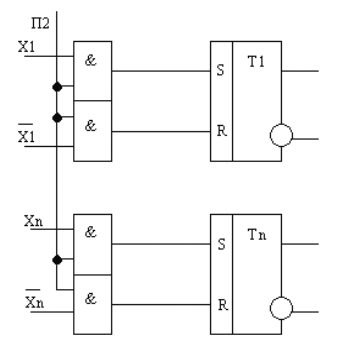

Схема прийому інформації в регістр без попередньої установки його в «0» представлена на рисунку 4.

Рис. 4 - Схема прийому інформації в регістр без попередньої установки його в «0»

Використання парафазного коду забезпечує установку тригерів в необхідний стан незалежно від тієї інформації, яка була записана на них раніше.

Регістром зсуву називається такий регістр, який виконує мікрооперацію зсуву, а також мікрооперації прийому та видачі слів.

Якщо дві останні операції реалізуються тільки в крайніх розрядах регістра (у першому або n-ому), то регістр зсуву називають також послідовним регістром.

При зсуві слова в регістрі розряди, що вийшли за межі розрядної сітки регістра, втрачаються, а розряди, що звільнилися, заповнюються нулями.

Регістри які можуть здійснювати зсув слова як вліво, так і вправо, називають реверсивними.

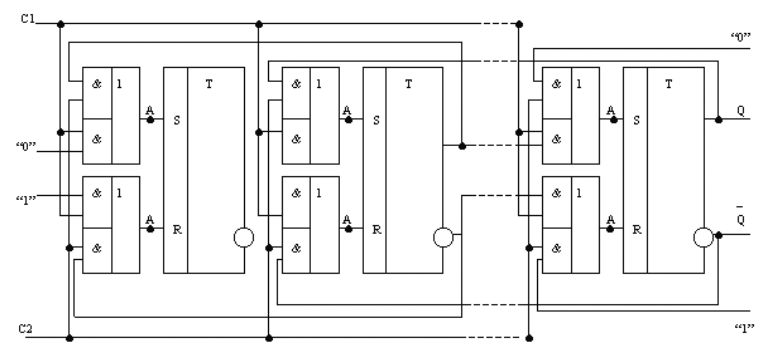

Схема реверсивного регістра зсуву з парафазною передачею слів зображена на рисунку 5.

Рис. 5 - Схема реверсивного регістра зсуву з парафазною передачею слів

де:

C1 - сигнал зсуву вмісту регістра вправо на один розряд;

С2 - сигнал зсуву вмісту регістра на один розряд вліво.

Схема реверсивного регістра зсуву з парафазною передачею слів не потребує скидання регістра в нуль.

Регістр зсуву реалізує перетворення послідовного коду в паралельний і навпаки. При перетворенні послідовного коду в паралельний, запис слова в регістр здійснюється синхронно з зсувом його вмісту вліво, якщо послідовний код поступає з старших розрядів, або вправо, якщо код поступає з молодших розрядів.

Після заповнення всіх розрядів слідує паралельна видача слова за допомогою елементів підключених до виходів тригерів регістра.

При перетворенні паралельного коду в послідовний інформація заноситься в регістр паралельним кодом, а потім слідує серія з п зсовуючих сигналів.

Послідовний код зчитується з тригера молодшого розряду при зсуві вправо, або з тригера старшого розряду при зсуві вліво.

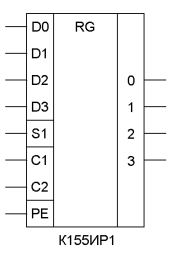

До складу 155 серії входить мікросхема 155ИР1 - чотирьохрозрядний регістр зсуву, умовне графічне зображення якого приведено на рисунку 6.

Рис. 6 - Умовне графічне зображення мікросхеми 155ИР1

Регістр зсуву має послідовний вхід даних 51, чотири паралельні входи D0-D3, а також чотири виходи Q0-Q3 від кожних з тригерів.

Регістр має два тактових входи С1 та С2. Від будь-якого з п'яти входів даних код поступить на виходи синхронно з негативним перепадом, поданим на один з тактових входів.

Вхід дозволу паралельного завантаження РЕ служить для вибору режиму роботи регістра.

Якщо на вхід РЕ подається напруга високого рівня, то дозволяється робота тактовому входу С2. У момент приходу на цей вхід негативного перепаду тактового імпульсу в регістр завантажуються дані від паралельних входів D0-D3.

Якщо на вхід РЕ подана напруга низького рівня, то дозволяється робота по тактовому входу С1. Негативні фронти тактових імпульсів зсовують дані, які надходять від послідовного входу S1, на вихід Q0, потім на Q1, Q2, Q3, тобто відбувається зсув вправо.

Зсув даних вліво здійснюється якщо з'єднати вихід Q3 та вхід D2, Q2 та D1, Q1 та

D0.

Регістр необхідно перевести в паралельний режим, подавши на вхід РЕ напругу високого рівня.

Напругу на вході РЕ можна міняти тільки у випадку якщо на обох тактових входах С1 та С2 рівні низькі. Проте, якщо на вході С1 напруга низького рівня, зміна сигналу на вході РЕ від низького рівня до високого не міняє стану виходів.

|

|