Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Демультиплексори

|

|

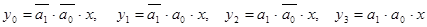

Демультиплексор (від англ. demultiplexer) – це комбінаційний цифровий вузол, який здійснює операцію передачі сигналу з одного інформаційного входу на один з виходів. Демультиплексор має тільки один інформаційний вхід x і k адресних входів ak-1, …, an, а також n=2k виходів. Наприклад, для демультиплексора при k=2, n=4 відповідна система рівнянь переходів буде мати вигляд:

(4)

(4)

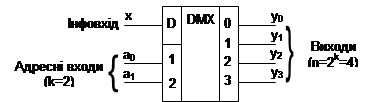

Порівнявши рівняння (4) і (3) можливо зробити висновок, що функцію демультиплексора реалізує стробуємий дешифратор у випадку, якщо на вхід C пожати інформаційний сигнал x, а входи дешифратора x1, x0 використати як адресні входи демультиплексора a1, a0 (C®x, x1®a1, x0®a0). Таблиця істинності для такого демультиплексора представлена в таблиці 2.

Таблиця 2. Таблиця істинності демультиплексора “1”®”4”

| Входи | Виходи | |||||

| інфо | адресні | y3 | y2 | y1 | y0 | |

| x | a1 | a0 | ||||

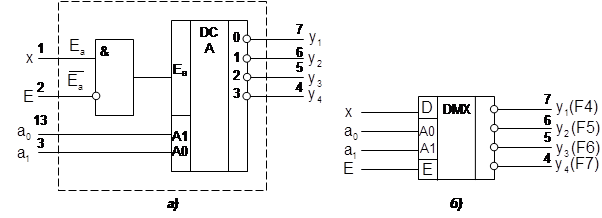

Відповідна структурна схема мультиплексора буде практично повторювати розглянуту вище схему дешифратора (рис.1.а) з введеною для демультиплексорів системою перепозначення функціонального призначення входів і виходів. Умовне графічне позначення демультиплексора “1®4” представлено на рис.3.

|

Рис.3. Умовне графічне позначення демультиплексора “1®4”

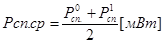

Завдання №1. Вивчення принципу роботи дешифратора “1®2”, побудованого на БЛЕ І-НІ.

1. Найпростіший одновходовий асинхронний дешифратор типу “1®2” дуже просто побудувати на БЛЕ 2І-НІ, які входять до складу МС К155ЛА3. Схема дешифратора “1®2” представлена на рис.4.а, а її апаратна реалізація на базі МС ТТЛ К155ЛА3 зображена на рис.4.б. При цьому використовуються тільки три БЛЕ з чотирьох, тобто незадіяний елемент DD1.4 переводиться у одиничний вихідний стан (на виходах 12, 13 – лог. 0).

2. На лабораторному стенді ЛС-02 скласти схему для дослідження дешифратора “1®2” (рис. 2.в). Встановити і зафіксувати МС К155ЛА3 в панельці на стенді. Включити живлення і за показами контрольних приладів (PA1 і PV1, включених в коло живлення МС як і в попередніх лабораторних роботах) визначити Iсп [мА] при напрузі живлення Uж [В]. Розрахувати Pсп.

3. Дослідити таблицю істинності дешифратора типу “1®2” (табл.3)

Таблиця 3. Таблиця істинності дешифратора типу “1®2”

| Вхід | Виходи | |||

| X | y1 | Uy1, В | y0 | Uy0, В |

| 1, 2, 4, 5 |

4. Виходячи з таблиці 3, записати систему рівнянь, яку відпрацьовує дешифратор “1®2”.

5. Визначити потужність споживання при x=0 і x=1 та розрахувати  .

.

|

Рис.4. Принципова електрична схема (а), умовне графічне позначення (б) і практична реалізація (в) DC “1®2”

Завдання 2. Вивчення принципу роботи дешифраторів і демультиплексорів на базі МС ТТЛ К155ИД4.

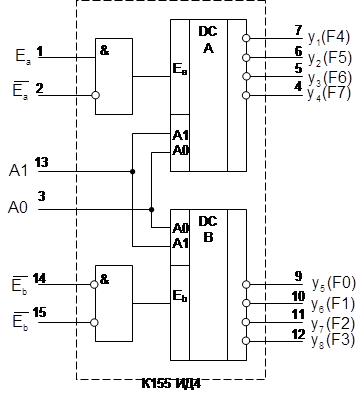

Внутрішня структура МС ТТЛ середнього ступеня інтеграції К155ИД4 представлена на рис.5. За своїм функціональним призначенням ця МС є універсальним дешифратором-демультиплексором і допускає різні варіанти її застосування.

|

Рис.5. Структурна схема дешифратора на основі МС ТТЛ К155ИД4

Структурна схема К155ИД4 включає в себе незалежні дешифратори, які можуть приймати дворозрядні коди адреси A0 і A1:

· перший дешифратор DC A має два роздільні входи дозволу – прямий Ea і інвертований  та два суміщені адресні входи A0 і A1;

та два суміщені адресні входи A0 і A1;

· другий дешифратор DC B має два розділені інвертовані входи дозволу  та два сумісні адресні входи A0 і A1.

та два сумісні адресні входи A0 і A1.

УВАГА! 1. Мікросхема К155ИД4 виконана у корпусі DIP-16, в якому +5В підключається до виваода 16, а 0В – відповідно, до вивода 8.

2. Всі виходи в цій мікросхемі інвертовані, тобто активним вихідним рівнем є рівень лог. 0.

2.1. Вивчення дешифратора типу “2®4” на основі МС ТТЛ К155ИД4.

1. Для побудови дешифратора типу “2®4” на основі К155ИД4 використовується лише половина цієї мікросхеми за схемою, яка представлена на рис.6.

|

Рис.6. Структурна схема реалізації дешифратора “2®4” на базі половини МС К155ИД4 (а) та його уомвне графічне позначення (б)

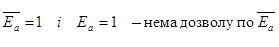

2. Сигнал дозволу роботи дешифратора  , як це випливає із схеми на рис.6.а, є рівним лог. 0 (

, як це випливає із схеми на рис.6.а, є рівним лог. 0 ( ), що можливо лише при наступній комбінації сигналів на роздільних входах МС:

), що можливо лише при наступній комбінації сигналів на роздільних входах МС:

(4)

(4)

в усіх інших випадках дешифратор працювати за відповідними рівняннями (1) не буде і на його виходах буде сигнал лог. 1. Такими випадками будуть наступні:

, (5)

, (5)

. (6)

. (6)

3. ВВести на стенд ЛС-02 картку з цокольовкою МС К155ИД4, вивчити її цокольовку. Скласти схему для досліджень дешифратора “2®4” (рис.6.а); встановити і зафіксувати мікросхему в панельці.

До виводів 8 і 16 підключити схему живлення з контрольними приладами PA1 і PV1.

4. Включити живлення і дослідити розширену таблицю істинності, що описує роботу дешифратора “2®4” (див. табл. 4).

Таблиці 4. Таблиця істинності дешифратора “2®4” на базі МС ТТЛ К155ИД4

| Інфовходи | Входи дозволу | Виходи yi (Fi) | Режим роботи | |||||

| x1 | x0 |

|

| y4 (F3) | y3 (F2) | y2 (F1) | y1 (F0) | |

| ´ | ´ | ´ | Нема дозволу по

| |||||

| Дозволений режим роботи DCA “2®4” | ||||||||

| ´ | ´ | ´ | Нема дозволу по

| |||||

| Номери виводів |

Примітка: При заповненні таблиці 4 експериментальними даними необхідно врахувати наступні особливості запису:

– позначення ´ означає довільне двійкове число (0 або 1);

– у стовпчиках yi (Fi) записується логічний стан і відповідна величина напруги [В], що вимірюється мультиметром PV2 M830B. Наприклад:  або

або

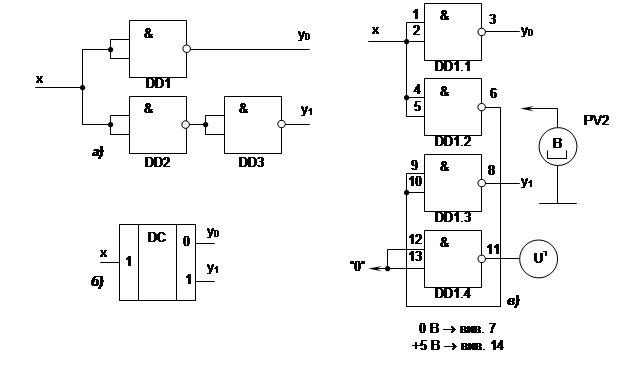

5. Під час проведення досліджень необхідно зафіксувати максимальний і мінімальний струм споживання, а також визначити середню споживану потужність в МС К155ИД4 в цьому режимі роботи за формулою:

(7)

(7)

6. Після дослідження таблиці істинності виключити живлення і розібрати зовнішні комутуючі провідники.

На підставі тої частини таблиці істинності, в якій МС виконувала функції дешифратора “2®4”, записати систему вихідних рівнянь yi.

2.2. Вивчення дешифратора типу “3®8” на базі МС К155ИД4.

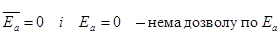

1. Для побудови повного дешифратора типу “3®8” необхідно використати обидва дешифратора DC A і DC B (див. рис. 5), виконати зовнішню комутацію входів та зробити необхідне перепозначення входів і виходів у відповідності зі схемами на рис.7.

2. Сигнал дозволу роботи обох дешифраторів E організовано шляхом паралельного з’єднання входів  і

і  . Активним сигналом, при якому дозволяється робота дешифратора, є E=0, в протилежному випадку реалізується режим заборони і на всіх виходах Fj зафіксується стан лог. 1, який не буде змінюватись при довільних комібнаціях інфосигналів x0, x1, x2. Додатковий інформаційний вхід x2 в такій схемі організовано шляхом сумісного використання входів дозволу

. Активним сигналом, при якому дозволяється робота дешифратора, є E=0, в протилежному випадку реалізується режим заборони і на всіх виходах Fj зафіксується стан лог. 1, який не буде змінюватись при довільних комібнаціях інфосигналів x0, x1, x2. Додатковий інформаційний вхід x2 в такій схемі організовано шляхом сумісного використання входів дозволу  і

і  .

.

3. Скласти схему для досліджень (рис.6.а), включити живлення і дослідити розширену таблицю істинності дешифратора типу “3®8” (таблиця 5).

Таблиця 5. Таблиця істинності повного дешифратора “3®8”.

| Інфовходи | Вхід дозволу | Виходи Fj | Режим роботи | |||||||||

| x2 | x1 | x0 |

| F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 | |

| ´ | ´ | ´ | Нема дозволу | |||||||||

| Дозволений режим роботи DC “3®8” | ||||||||||||

| 1, 14 | 2, 15 | Номери виводів |

|

Рис.7. Схема побудови дешифратора “3®8” на базі МС К155ИД4 (а) і його умовне графічне позначення

4. Під час проведення досліджень необхідно зафіксувати максимальний і мінімальний струм споживання, а також визначити середню споживану потужність МС К155ИД4 в цьому режимі роботи за формулою (7).

5. Після закінчення досліджень виключити живлення і розібрати зовнішні комутаційні з’єднання.

На підставі тої частини таблиці істинності, в якій МС виконує функції дешифратора “3®8”, записати систему вихідних рівнянь Fj.

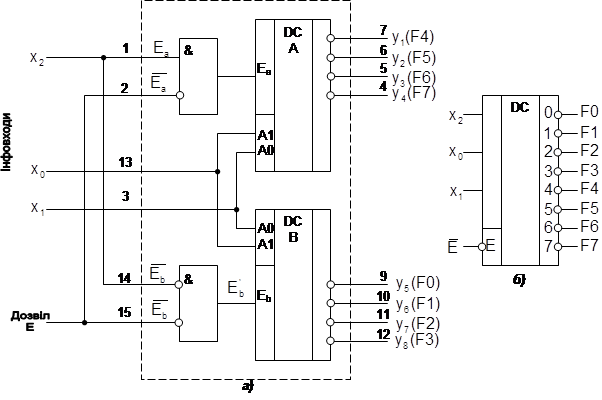

2.3. Вивчення мультиплексора типу “1®4” на основі МС ТТЛ К155ИД4.

1. Для побудови демультиплексора типу “1®4” використовуєтьс половина МС К155ИД4, а точніше лише схема з дешифратором DC A (див. рис.6). При цьому вихідна схема дешифратора не потребує додаткових зовнішніх з’єднань і необхідно виконати тільки комутаційне перепозначення функціонального призначення виводів. Для цього необхідно виконати наступні перепозначення (див. схему на рис.8):

– провід x, на якому має бути зафікосваний рівень лог. 0, що передається на вихідні виводи yi, організується на базі входу дозволу  (вивід 2);

(вивід 2);

– вхід дозволу для демультиплексора E залишається функціонально прив’язаним до входу дозволу DCA Ea (вивід 1);

– адресні виводи демультиплексора a0, a1 призначаються без зміни індекса адресних входів дешифратора A0, A1.

Рис.8. Схема побудови демультиплексора типу “1®4” на базі МС К155ИД4 (а) та його умовне позначення (б)

2. Скласти схему для дослідження демультиплексора (рис. 8), включити живлення і дослідити розширену таблицю істинності (таблиця 6).

Таблиця 6. Таблиця істинности демультиплексора типу “1®4”

| Адресні входи | Інфовхід | Вхід дозволу | Виходу yi | Режим роботи | ||||

| a1 | a0 | x | E | y4 | y3 | y2 | y1 | |

| ´ | ´ | ´ | Нема дозволу по

| |||||

| Дозволений режим роботи DCA “2®4” | ||||||||

| ´ | ´ | ´ | Нема дозволу по

| |||||

| Номери виводів |

3. Під час проведення досліджень необхідно зафіксувати максимальний та мінімальний струми споживання, а також визначити середню споживану потужність МС К155ИД4 в цьому режимі роботи за формулою (7).

4. Після закінчення досліджень виключити живлення і розібрати щовнішні комутаційні з’єднання.

Для дозволеного режиму роботи демультиплексора записати систему вихідних рівнянь yi.

|

|