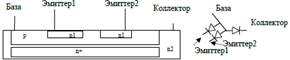

3. Быстродействие

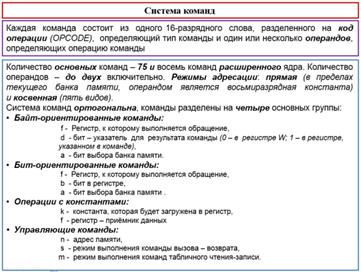

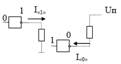

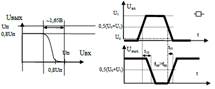

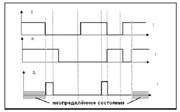

Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного. Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

3. Быстродействие

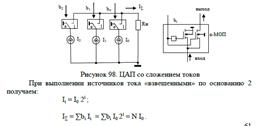

Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного. Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

Таким образом, частотные свойства цифрового элемента определяют, в-основном, по времени задержки.

РТЛ - инвертор

Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером.

РТЛ элемент 2ИЛИ-НЕ

Базисный элемент 2ИЛИ-НЕ (стрелка Пирса) резисторно-транзисторной логики содержит два npn – транзистора.

Таким образом, частотные свойства цифрового элемента определяют, в-основном, по времени задержки.

РТЛ - инвертор

Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером.

РТЛ элемент 2ИЛИ-НЕ

Базисный элемент 2ИЛИ-НЕ (стрелка Пирса) резисторно-транзисторной логики содержит два npn – транзистора.  РТЛ элемент 2И-НЕ

Базисный элемент 2И-НЕ (штрих Шеффера) резисторно-транзисторной логики также содержит два npn – транзистора.

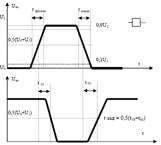

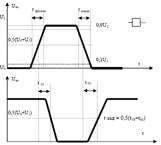

ДТЛ элемент 2И-НЕ

В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0, 6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0, 6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

РТЛ элемент 2И-НЕ

Базисный элемент 2И-НЕ (штрих Шеффера) резисторно-транзисторной логики также содержит два npn – транзистора.

ДТЛ элемент 2И-НЕ

В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0, 6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0, 6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

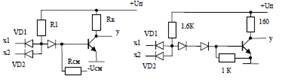

Упрощенная ДТЛ 2И-НЕ.Модифицированный элемент ДТЛ

два изменения: дополнительный последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов.

Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде).

Упрощенная ДТЛ 2И-НЕ.Модифицированный элемент ДТЛ

два изменения: дополнительный последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов.

Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде).

| 3. ТТЛ элемент 2И-НЕ

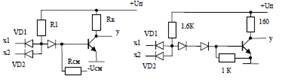

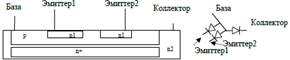

Если в конструкции биполярного транзистора предусмотреть не один, а несколько эмиттеров (обычно 5-8), появляется возможность использовать его в качестве входного каскада. Этим существенно упрощается и удешевляется схема логических элементов, использующих такого рода многоэмиттерный транзистор (МЭТ).

Для исключения паразитных горизонтальных цепочек эмиттер1-база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

Для исключения паразитных горизонтальных цепочек эмиттер1-база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

схемой с простым инвертором и обладает существенными недостатками: низкая помехоустойчивость; малая нагрузочная способность; ограниченное быстродействие при работе на емкостную нагрузку.

Быстродействие логического элемента в значительной степени определяется продолжительностью t01 – переключения транзистора из открытого режима в режим отсечки. В действительности транзистор начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов. Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора. схемой с простым инвертором и обладает существенными недостатками: низкая помехоустойчивость; малая нагрузочная способность; ограниченное быстродействие при работе на емкостную нагрузку.

Быстродействие логического элемента в значительной степени определяется продолжительностью t01 – переключения транзистора из открытого режима в режим отсечки. В действительности транзистор начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов. Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора.

Особенностью схемы является подбор сопротивлений R3 > > R4. При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение.

Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ.Структурно схема состоит из трёх блоков: входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4). При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0, 8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2, б-э VT4 (для этого нужно не менее 0, 6 х 3 = 1, 8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он

также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min.

При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1, 2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1, 2 В) и коллектора VT4 (около 0, 3 В) Δ U< 0, 9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0, 3 В. Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны.

Особенностью схемы является подбор сопротивлений R3 > > R4. При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение.

Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ.Структурно схема состоит из трёх блоков: входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4). При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0, 8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2, б-э VT4 (для этого нужно не менее 0, 6 х 3 = 1, 8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он

также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min.

При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1, 2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1, 2 В) и коллектора VT4 (около 0, 3 В) Δ U< 0, 9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0, 3 В. Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны.

|

Основные параметры логических элементов (на примере инвертора)

1. Токи (инвертор работает на элемент ДТЛ)

I«1» max < < I «0» max

Основные параметры логических элементов (на примере инвертора)

1. Токи (инвертор работает на элемент ДТЛ)

I«1» max < < I «0» max

2.Напряжения

Для повышения помехоустойчивости выдерживаются следующие соотношения (для ТТЛ-уровней):

2В < = Uвх «1» min < Uвых «1» min

Uвых «0» max < Uвх «0» max < = 0, 8 В

Говорят, что «выходные» напряжения должны быть «лучше» входных, т.е. интервал выходных напряжений является охватывающим для интервала входных напряжений.

2.Напряжения

Для повышения помехоустойчивости выдерживаются следующие соотношения (для ТТЛ-уровней):

2В < = Uвх «1» min < Uвых «1» min

Uвых «0» max < Uвх «0» max < = 0, 8 В

Говорят, что «выходные» напряжения должны быть «лучше» входных, т.е. интервал выходных напряжений является охватывающим для интервала входных напряжений.

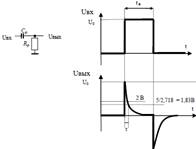

3. Быстродействие

Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного. Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

3. Быстродействие

Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного. Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

Таким образом, частотные свойства цифрового элемента определяют, в-основном, по времени задержки.

РТЛ - инвертор

Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером.

РТЛ элемент 2ИЛИ-НЕ

Базисный элемент 2ИЛИ-НЕ (стрелка Пирса) резисторно-транзисторной логики содержит два npn – транзистора.

Таким образом, частотные свойства цифрового элемента определяют, в-основном, по времени задержки.

РТЛ - инвертор

Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером.

РТЛ элемент 2ИЛИ-НЕ

Базисный элемент 2ИЛИ-НЕ (стрелка Пирса) резисторно-транзисторной логики содержит два npn – транзистора.  РТЛ элемент 2И-НЕ

Базисный элемент 2И-НЕ (штрих Шеффера) резисторно-транзисторной логики также содержит два npn – транзистора.

ДТЛ элемент 2И-НЕ

В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0, 6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0, 6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

РТЛ элемент 2И-НЕ

Базисный элемент 2И-НЕ (штрих Шеффера) резисторно-транзисторной логики также содержит два npn – транзистора.

ДТЛ элемент 2И-НЕ

В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0, 6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0, 6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

Упрощенная ДТЛ 2И-НЕ.Модифицированный элемент ДТЛ

два изменения: дополнительный последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов.

Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде).

Упрощенная ДТЛ 2И-НЕ.Модифицированный элемент ДТЛ

два изменения: дополнительный последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов.

Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде).

Для исключения паразитных горизонтальных цепочек эмиттер1-база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

Для исключения паразитных горизонтальных цепочек эмиттер1-база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

схемой с простым инвертором и обладает существенными недостатками: низкая помехоустойчивость; малая нагрузочная способность; ограниченное быстродействие при работе на емкостную нагрузку.

Быстродействие логического элемента в значительной степени определяется продолжительностью t01 – переключения транзистора из открытого режима в режим отсечки. В действительности транзистор начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов. Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора.

схемой с простым инвертором и обладает существенными недостатками: низкая помехоустойчивость; малая нагрузочная способность; ограниченное быстродействие при работе на емкостную нагрузку.

Быстродействие логического элемента в значительной степени определяется продолжительностью t01 – переключения транзистора из открытого режима в режим отсечки. В действительности транзистор начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов. Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора.

Особенностью схемы является подбор сопротивлений R3 > > R4. При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение.

Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ.Структурно схема состоит из трёх блоков: входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4). При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0, 8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2, б-э VT4 (для этого нужно не менее 0, 6 х 3 = 1, 8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он

также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min.

При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1, 2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1, 2 В) и коллектора VT4 (около 0, 3 В) Δ U< 0, 9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0, 3 В. Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны.

Особенностью схемы является подбор сопротивлений R3 > > R4. При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение.

Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ.Структурно схема состоит из трёх блоков: входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4). При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0, 8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2, б-э VT4 (для этого нужно не менее 0, 6 х 3 = 1, 8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он

также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min.

При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1, 2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1, 2 В) и коллектора VT4 (около 0, 3 В) Δ U< 0, 9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0, 3 В. Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны.

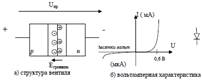

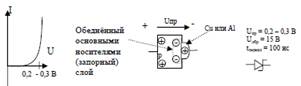

Конструкция, основные параметры, вольт-амперная характеристика и условное обозначение диода Шоттки

Конструкция, основные параметры, вольт-амперная характеристика и условное обозначение диода Шоттки

Схема шунтирования база – коллекторного перехода ключевого транзистора Упрощенная схема базового элемента ТТЛШ

Отмечают, что энергопотребление схем ТТЛШ не менее, чем в 5 раз ниже, чем ТТЛ, что позволяет только за счёт этого значительно повысить степень интеграции

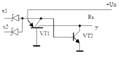

ИИЛ элемент

Наличие в схеме резисторов определяет достаточно серьёзные проблемы при изготовлении интегральных схем, т.к. напыление металла или сплава технологически сложно и достаточно дорого. Решением проблемы может стать замена резисторов нормально открытыми транзисторами.

Процесс подобной модернизации схемы рассмотрим на примере РТЛ – инвертора. Резисторы Rк и Rб можно рассматривать, как источники, соответственно базового и коллекторного тока. Вместо них в данном случае в схему включают pnp – транзисторы.

Схема шунтирования база – коллекторного перехода ключевого транзистора Упрощенная схема базового элемента ТТЛШ

Отмечают, что энергопотребление схем ТТЛШ не менее, чем в 5 раз ниже, чем ТТЛ, что позволяет только за счёт этого значительно повысить степень интеграции

ИИЛ элемент

Наличие в схеме резисторов определяет достаточно серьёзные проблемы при изготовлении интегральных схем, т.к. напыление металла или сплава технологически сложно и достаточно дорого. Решением проблемы может стать замена резисторов нормально открытыми транзисторами.

Процесс подобной модернизации схемы рассмотрим на примере РТЛ – инвертора. Резисторы Rк и Rб можно рассматривать, как источники, соответственно базового и коллекторного тока. Вместо них в данном случае в схему включают pnp – транзисторы.

Для входных линий в элементах ИИЛ обычно используются диоды Шоттки, а транзисторы, выполняющие роль источников тока, объединяют в один: Конструктивно многоколлекторный транзистор подобен многоэмиттерному, включенному по инверсной схеме. Однако при его изготовлении принимаются специальные меры для увеличения коэффициента усиления в расчёте на каждый коллектор до требуемого уровня (сокращение расстояния между коллекторами, приближение скрытого слоя повышенной концентрации в области эмиттера к слою базы).

Для входных линий в элементах ИИЛ обычно используются диоды Шоттки, а транзисторы, выполняющие роль источников тока, объединяют в один: Конструктивно многоколлекторный транзистор подобен многоэмиттерному, включенному по инверсной схеме. Однако при его изготовлении принимаются специальные меры для увеличения коэффициента усиления в расчёте на каждый коллектор до требуемого уровня (сокращение расстояния между коллекторами, приближение скрытого слоя повышенной концентрации в области эмиттера к слою базы).

Инвертор и базисный элемент эмиттерно-связной логики

Иной вариант удерживания транзистора, формирующего выходной сигнал, на границе насыщенного состояния реализован, в так называемой, эмиттерно-связной логике (ЭСЛ). В основе её лежит дифференциальная схема включения npn – транзисторов (токовый ключ).

Транзисторы VT1 и VT2 выполняют с максимально близкими параметрами. Опорное напряжение (Uоп) ключа подбирается такого номинала, при котором за вычетом падения напряжения на Rэ (Uа), оставшееся (Uбэ2) соответствовало бы начальной стадии открытия база-коллекторного перехода (0, 6 В). Пока напряжение

Uвх = Uбэ1+ Uа < Uоп = Uбэ2+ Uа; Uбэ1 < Uбэ2.

Инвертор и базисный элемент эмиттерно-связной логики

Иной вариант удерживания транзистора, формирующего выходной сигнал, на границе насыщенного состояния реализован, в так называемой, эмиттерно-связной логике (ЭСЛ). В основе её лежит дифференциальная схема включения npn – транзисторов (токовый ключ).

Транзисторы VT1 и VT2 выполняют с максимально близкими параметрами. Опорное напряжение (Uоп) ключа подбирается такого номинала, при котором за вычетом падения напряжения на Rэ (Uа), оставшееся (Uбэ2) соответствовало бы начальной стадии открытия база-коллекторного перехода (0, 6 В). Пока напряжение

Uвх = Uбэ1+ Uа < Uоп = Uбэ2+ Uа; Uбэ1 < Uбэ2.

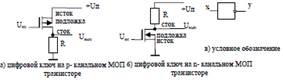

Наиболее распространённой является схема включения полевого транзистора с общим истоком.

Наиболее распространённой является схема включения полевого транзистора с общим истоком.

Уровни сигналов МОП (и КМОП) элементов приняты следующими: U0< =0, 5 U1> =0, 8Uп

затвора относительно подложки), при котором индуцируется канал составляет от 0, 3 до 3В (среднее 1, 65В). Для p – канального транзистора затвор должен быть отрицательнее подложки, а для n- канального – положительнее.

Для формирования единичного уровня сигнала на выходе в схемах МОП – ключа (рисунок 29, а) необходимо дополнительное сопротивление R.

Его значение можно оценить из следующих предположений. Пусть при Uпит = 5В необходимо обеспечить уровень U1 = 0, 8 Uпит = 4В, считая сопротивление открытого канала равным 10 кОм (в различных вариантах от 1 до 15 кОм). Выходное напряжение в открытом состоянии транзистора формируется резистивным делителем: При переключении в закрытое состояние это сопротивление входит в цепь, по которой стекает отрицательный заряд затвора, ограничивает значение разрядного тока и увеличивает продолжительность формирования нулевого сигнала на выходе элемента. По этой причине максимальная частота МОП – элемента ограничивается значением в несколько сотен кГц.

Уровни сигналов МОП (и КМОП) элементов приняты следующими: U0< =0, 5 U1> =0, 8Uп

затвора относительно подложки), при котором индуцируется канал составляет от 0, 3 до 3В (среднее 1, 65В). Для p – канального транзистора затвор должен быть отрицательнее подложки, а для n- канального – положительнее.

Для формирования единичного уровня сигнала на выходе в схемах МОП – ключа (рисунок 29, а) необходимо дополнительное сопротивление R.

Его значение можно оценить из следующих предположений. Пусть при Uпит = 5В необходимо обеспечить уровень U1 = 0, 8 Uпит = 4В, считая сопротивление открытого канала равным 10 кОм (в различных вариантах от 1 до 15 кОм). Выходное напряжение в открытом состоянии транзистора формируется резистивным делителем: При переключении в закрытое состояние это сопротивление входит в цепь, по которой стекает отрицательный заряд затвора, ограничивает значение разрядного тока и увеличивает продолжительность формирования нулевого сигнала на выходе элемента. По этой причине максимальная частота МОП – элемента ограничивается значением в несколько сотен кГц.

Базисные элементы pМОП – логики в несколько упрощенном варианте представлены на рисунке 37. Роль дополнительного сопротивления выполняют в данном случае постоянно открытые транзисторы VT3. Для повышения быстродействия схемы используют пару разноканальных (взаимно дополняющих, т.е. комплементарных) МОП – транзисторов. Подобная схема включения положена в основу КМОП – логики.

Базисные элементы pМОП – логики в несколько упрощенном варианте представлены на рисунке 37. Роль дополнительного сопротивления выполняют в данном случае постоянно открытые транзисторы VT3. Для повышения быстродействия схемы используют пару разноканальных (взаимно дополняющих, т.е. комплементарных) МОП – транзисторов. Подобная схема включения положена в основу КМОП – логики.

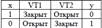

Состояния КМОП-И

Состояния КМОП-И  В схеме КМОП – инвертора единичный уровень сигнала формируется сопротивлением канала VT1 (и сопротивлением нагрузки, конечно), а нулевой уровень обеспечивается открытым транзистором VT2. В момент переключения один из транзисторов обеспечивает путь с меньшим сопротивлением для стекания заряда с затвора другого. Переключение происходит быстрее и поэтому рабочая частота КМОП - элементов находится в мегагерцовом диапазоне.

В схеме КМОП – инвертора единичный уровень сигнала формируется сопротивлением канала VT1 (и сопротивлением нагрузки, конечно), а нулевой уровень обеспечивается открытым транзистором VT2. В момент переключения один из транзисторов обеспечивает путь с меньшим сопротивлением для стекания заряда с затвора другого. Переключение происходит быстрее и поэтому рабочая частота КМОП - элементов находится в мегагерцовом диапазоне.

Базисные элементы КМОП – Л

В схемах базисных элементов одна пара транзисторов включена параллельно, а другая - ярусно.

Комплементарное включение полевых транзисторов используется также в схеме буферного элемента с высокоимпедансным состоянием. Данный элемент используется для объединения на некоторой общей шине произвольного количества отдельных устройств. Буферный элемент с высокоимпедансным состоянием:

Базисные элементы КМОП – Л

В схемах базисных элементов одна пара транзисторов включена параллельно, а другая - ярусно.

Комплементарное включение полевых транзисторов используется также в схеме буферного элемента с высокоимпедансным состоянием. Данный элемент используется для объединения на некоторой общей шине произвольного количества отдельных устройств. Буферный элемент с высокоимпедансным состоянием:

В структуре цифровых автоматов (ЦА) имеется блок запоминающих элементов (ЗЭ). По этой причине цифровые автоматы обладают конечным набором внутренних состояний (в данном случае, 2к). Внутренние состояния ЗЭ могут изменяться под действием входных сигналов. Выходной сигнал цифрового автомата формируется на основе входных сигналов и внутреннего состояния ЦА. Зачастую в качестве входных и выходных каскадов ЦА применяются соответствующие комбинационные схемы. Элементарными ЦА являются триггеры. Многочисленные устройства памяти также относятся к цифровым автоматам. Закон функционирования ЦА может быть также задан аналитически, но чаще для этого используются операционные таблицы (похожи на таблицы состояний КС) или временные диаграммы.

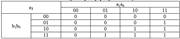

Комбинационные схемы

Знакомство с комбинационными схемами будет иллюстрироваться созданием их с помощью технологии цифрового синтеза на базе карт Карно.

Как известно, картой Карно называется двумерная таблица логических функций, в каждой клетке которой находится произведение входных переменных или их инверсий. Сами переменные идентифицируют строки и столбцы этой таблицы. Используется карта Карно при числе переменных до 6. Алгебраически карта Карно соответствует записи логической (передаточной) функции в совершенной дизъюнктивной нормальной форме (СДНФ):

F = Σ fi mi

для i = 0, 1 …, q-1,

где

fi - значение (требуемое) передаточной функции,

mi - минтерм или конъюнкция переменных

q = 2k - количество минтермов,

k – количество входных переменных

Иначе говоря, минтермы представляет собой все возможные комбинации входных сигналов, а с помощью fi выделяются те сочетания, которые должны формировать единичный результат.

Полученную передаточную функцию, как правило, оптимизируют с целью сокращения операций. При этом могут быть использованы, как аналитические выражения для основных логических функций

В структуре цифровых автоматов (ЦА) имеется блок запоминающих элементов (ЗЭ). По этой причине цифровые автоматы обладают конечным набором внутренних состояний (в данном случае, 2к). Внутренние состояния ЗЭ могут изменяться под действием входных сигналов. Выходной сигнал цифрового автомата формируется на основе входных сигналов и внутреннего состояния ЦА. Зачастую в качестве входных и выходных каскадов ЦА применяются соответствующие комбинационные схемы. Элементарными ЦА являются триггеры. Многочисленные устройства памяти также относятся к цифровым автоматам. Закон функционирования ЦА может быть также задан аналитически, но чаще для этого используются операционные таблицы (похожи на таблицы состояний КС) или временные диаграммы.

Комбинационные схемы

Знакомство с комбинационными схемами будет иллюстрироваться созданием их с помощью технологии цифрового синтеза на базе карт Карно.

Как известно, картой Карно называется двумерная таблица логических функций, в каждой клетке которой находится произведение входных переменных или их инверсий. Сами переменные идентифицируют строки и столбцы этой таблицы. Используется карта Карно при числе переменных до 6. Алгебраически карта Карно соответствует записи логической (передаточной) функции в совершенной дизъюнктивной нормальной форме (СДНФ):

F = Σ fi mi

для i = 0, 1 …, q-1,

где

fi - значение (требуемое) передаточной функции,

mi - минтерм или конъюнкция переменных

q = 2k - количество минтермов,

k – количество входных переменных

Иначе говоря, минтермы представляет собой все возможные комбинации входных сигналов, а с помощью fi выделяются те сочетания, которые должны формировать единичный результат.

Полученную передаточную функцию, как правило, оптимизируют с целью сокращения операций. При этом могут быть использованы, как аналитические выражения для основных логических функций

Карта Карно одноразразрядного сумматора для выхода s

Карта Карно одноразразрядного сумматора для выхода s

Передаточная функция до преобразования:

Передаточная функция до преобразования:

Передаточная функция после преобразования:

Передаточная функция после преобразования:

При этом выражение в первой скобке соответствует логической функции «исключающее ИЛИ», а во второй - «исключающее ИЛИ-НЕ». Таким образом, относительно входа с и результата операции «исключающее ИЛИ» для входов a и b передаточная функция представляет собой ещё одну операцию «исключающее ИЛИ».

При этом выражение в первой скобке соответствует логической функции «исключающее ИЛИ», а во второй - «исключающее ИЛИ-НЕ». Таким образом, относительно входа с и результата операции «исключающее ИЛИ» для входов a и b передаточная функция представляет собой ещё одну операцию «исключающее ИЛИ».

Достоинством схемы последовательного суммирования является простота и наглядность, недостатком - достаточно существенная задержка в формировании результата, равная n tзад, где tзад - время задержки выходных сигналов одноразрядного сумматора. Иначе данную схему называют сложением с переносом вдоль разрядной сетки.

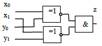

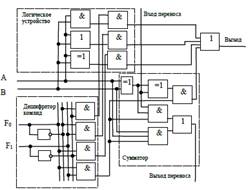

Сумматор с параллельным переносом

Для увеличения быстродействия могут быть использована схема суммирования с параллельным переносом, в которой переносы определяются одновременно для всех разрядов с помощью специальных формирователей. При этом сами сумматоры выполняются упрощенно, так как формируют только сумму.

Формирователем переноса для нулевых разрядов слагаемых (с0), фактически, служит элемент «И» (рисунок). Каждый последующий формирователь имеет на два входа больше и, соответственно, более сложную схему. Самый старший формирователь (сn-2) для n- разрядных слагаемых имеет 2*(n-1) входов. Время задержки определяется по его задержке + по задержке упрощенного сумматора. Как следует из схемы, в качестве разрядных сумматоров могут быть использованы одноразрядные сумматоры, из которых исключены цепи, формирующие сигнал переноса

Достоинством схемы последовательного суммирования является простота и наглядность, недостатком - достаточно существенная задержка в формировании результата, равная n tзад, где tзад - время задержки выходных сигналов одноразрядного сумматора. Иначе данную схему называют сложением с переносом вдоль разрядной сетки.

Сумматор с параллельным переносом

Для увеличения быстродействия могут быть использована схема суммирования с параллельным переносом, в которой переносы определяются одновременно для всех разрядов с помощью специальных формирователей. При этом сами сумматоры выполняются упрощенно, так как формируют только сумму.

Формирователем переноса для нулевых разрядов слагаемых (с0), фактически, служит элемент «И» (рисунок). Каждый последующий формирователь имеет на два входа больше и, соответственно, более сложную схему. Самый старший формирователь (сn-2) для n- разрядных слагаемых имеет 2*(n-1) входов. Время задержки определяется по его задержке + по задержке упрощенного сумматора. Как следует из схемы, в качестве разрядных сумматоров могут быть использованы одноразрядные сумматоры, из которых исключены цепи, формирующие сигнал переноса  Формирователь переноса с0 для сумматора в первом разряде имеет два входа и представляет собой обычный элемент «И». Однако для каждого последующего разряда число входных линий увеличивается на 2 и, соответственно, усложняется схема. В частности, схема формирователя с1 может быть получена обычным образом:

Формирователь переноса с0 для сумматора в первом разряде имеет два входа и представляет собой обычный элемент «И». Однако для каждого последующего разряда число входных линий увеличивается на 2 и, соответственно, усложняется схема. В частности, схема формирователя с1 может быть получена обычным образом:

После небольших преобразований передаточной функции, записанной по карте Карно, реализующая её схема выглядит следующим образом.

Сумматор с условным переносом

Обычно в качестве 4-х разрядных сумматоров используются схемы последовательного переноса. В таком случае цепь переносов укорачивается вдвое.

После небольших преобразований передаточной функции, записанной по карте Карно, реализующая её схема выглядит следующим образом.

Сумматор с условным переносом

Обычно в качестве 4-х разрядных сумматоров используются схемы последовательного переноса. В таком случае цепь переносов укорачивается вдвое.

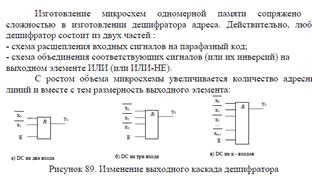

Три вида дешифраторов: - Линейные. - Пирамидальные.

- Многоступенчатые.

Три вида дешифраторов: - Линейные. - Пирамидальные.

- Многоступенчатые.

Двухразрядный компаратор равенство

Двухразрядный компаратор равенство

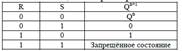

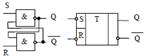

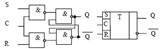

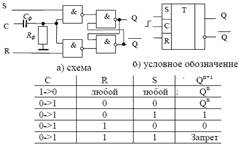

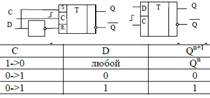

Основу любого триггера составляет т.н. последовательностная схема, которая может принимать одно из двух стабильных состояний. Для управления состояниями данной схемы инверторы заменяют на базисные элементы и получается асинхронный триггер.

Асинхронный RS-триггер

– Тригер, у которого имеются только информационные (логические) входы. Срабатывает непосредственно за изменением сигнала на входах, не считая времени задержки.

При подаче единицы на вход S (установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы не определено и зависит от реализации, например в триггере на элементах «или-не» оба выхода переходят в состояние логического «0», которое является неустойчивым и переходит в одно из устойчивых состояний при снятии управляющего сигнала с одного из входов.

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

Недостатком асинхронного RS – триггера является наличие т.н. запрещённого состояния или недопустимой комбинации входных сигналов. Конкретное сочетание установочных входов при этом зависит от того на каком базисе выполнен триггер.

Основу любого триггера составляет т.н. последовательностная схема, которая может принимать одно из двух стабильных состояний. Для управления состояниями данной схемы инверторы заменяют на базисные элементы и получается асинхронный триггер.

Асинхронный RS-триггер

– Тригер, у которого имеются только информационные (логические) входы. Срабатывает непосредственно за изменением сигнала на входах, не считая времени задержки.

При подаче единицы на вход S (установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы не определено и зависит от реализации, например в триггере на элементах «или-не» оба выхода переходят в состояние логического «0», которое является неустойчивым и переходит в одно из устойчивых состояний при снятии управляющего сигнала с одного из входов.

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

Недостатком асинхронного RS – триггера является наличие т.н. запрещённого состояния или недопустимой комбинации входных сигналов. Конкретное сочетание установочных входов при этом зависит от того на каком базисе выполнен триггер.

RS- триггера на базисе Пирса.

RS- триггера на базисе Пирса.

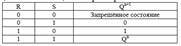

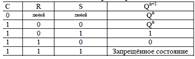

RS- триггер на базисе Шеффера

RS- триггер на базисе Шеффера

триггера на базисе Шеффера

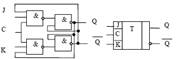

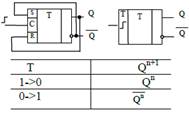

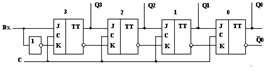

Статический JK – триггер - работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. Схема и условное изображение JK – триггера на базисе Шеффера

триггера на базисе Шеффера

Статический JK – триггер - работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. Схема и условное изображение JK – триггера на базисе Шеффера

Динамический однотактный CRS- триггер. С входной СR - цепью

Первым вариантом CRS – триггера с динамическим управлением считается схема с дифференцирующим каскадом. Как известно, схема CR – фильтра выполняет дифференцирование входного напряжения:

Uвых(t) = d/dt(Uвх(t));

τ = Rф Сф < < tи;

Uвых(t) = U0 e-t/τ, где U0 - значение напряжения при t = 0.

Динамический однотактный CRS- триггер. С входной СR - цепью

Первым вариантом CRS – триггера с динамическим управлением считается схема с дифференцирующим каскадом. Как известно, схема CR – фильтра выполняет дифференцирование входного напряжения:

Uвых(t) = d/dt(Uвх(t));

τ = Rф Сф < < tи;

Uвых(t) = U0 e-t/τ, где U0 - значение напряжения при t = 0.

Работу CR – цепи можно объяснить вторым правилом коммутации: Uc(-0) = Uc(0+)

Всё приложенное к ёмкости входное напр. в первый момент передаётся на выход (ёмкость в момент смены напр. ведёт себя, как закоротка).

Работу CR – цепи можно объяснить вторым правилом коммутации: Uc(-0) = Uc(0+)

Всё приложенное к ёмкости входное напр. в первый момент передаётся на выход (ёмкость в момент смены напр. ведёт себя, как закоротка).

Динамический двухтактный CRS- триггер

- триггер состоит из двух однотактных, называемых, соответственно мастер и помощник (master-slave).

Динамический двухтактный CRS- триггер

- триггер состоит из двух однотактных, называемых, соответственно мастер и помощник (master-slave).

Т - триггер выполняется на базе CRS – триггера, охваченного перекрёстными обратными связями.

Т - триггер выполняется на базе CRS – триггера, охваченного перекрёстными обратными связями.

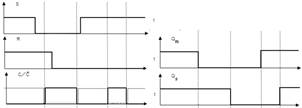

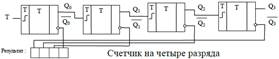

Регистры

Регистр - упорядоченная последовательность триггеров, предназначенная для хранения слов и выполнения микроопераций над ними.

Регистры могут быть однотактные и многотактные, параллельные и последовательные, сдвигающие, однофазные и парафазные, с динамическим или статическим управлением. Элементом регистра является триггер.

Рассмотрим действие регистра при записи в него числа 0011, начиная с правого - младшего - разряда. До записи числа все триггеры устанавливают в нулевое состояние. Затем на вход схемы подается серия импульсов, соответствующая записываемому числу, а на вход С подаются тактовые импульсы. Сначала на вход поступает импульс, соответствующий первому из записываемых разрядов. В конце тактового импульса он дает Q3 = 1 на выходе левого триггера. В конце следующего тактового импульса информационный импульс продвигается на выход следующего триггера и т. д. Одновременно продвигаются вправо и другие цифры записываемого числа. После прихода четырех тактовых импульсов все число оказывается записанным в четырех триггерах, причем старший разряд числа записи в левом триггере, а младший - в правом. Чтобы записанная информация сохранилась, дальнейший сдвиг прекращается. Это осуществляется прекращением подачи тактовых импульсов. Описанный регистр называется регистром сдвига с последовательным приемом информации.

Регистры

Регистр - упорядоченная последовательность триггеров, предназначенная для хранения слов и выполнения микроопераций над ними.

Регистры могут быть однотактные и многотактные, параллельные и последовательные, сдвигающие, однофазные и парафазные, с динамическим или статическим управлением. Элементом регистра является триггер.

Рассмотрим действие регистра при записи в него числа 0011, начиная с правого - младшего - разряда. До записи числа все триггеры устанавливают в нулевое состояние. Затем на вход схемы подается серия импульсов, соответствующая записываемому числу, а на вход С подаются тактовые импульсы. Сначала на вход поступает импульс, соответствующий первому из записываемых разрядов. В конце тактового импульса он дает Q3 = 1 на выходе левого триггера. В конце следующего тактового импульса информационный импульс продвигается на выход следующего триггера и т. д. Одновременно продвигаются вправо и другие цифры записываемого числа. После прихода четырех тактовых импульсов все число оказывается записанным в четырех триггерах, причем старший разряд числа записи в левом триггере, а младший - в правом. Чтобы записанная информация сохранилась, дальнейший сдвиг прекращается. Это осуществляется прекращением подачи тактовых импульсов. Описанный регистр называется регистром сдвига с последовательным приемом информации.

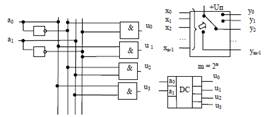

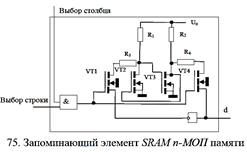

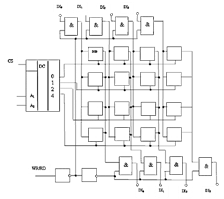

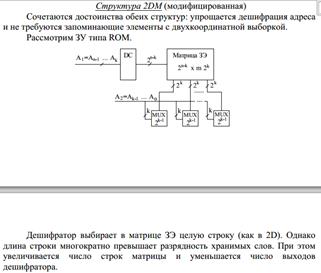

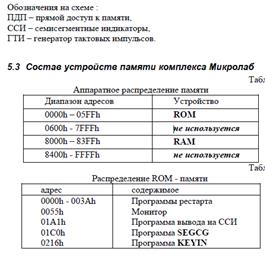

ЗУ (М=16, организация 4х4) с одномерной адресацией. Данная структура содержит матрицу 4х4 ЭЗЭ, каждый из которых снабжен тремя выводами: входом информации (IN)выходом информации (OFF) и входом разрешения работы – выбора кристалла (ES- ciment select), дешифратор адреса, входные и выходные ключи на элементах 2И.

Если на вход дешифратора подано некоторое адресное слово, на соответствующем его выходе формируется сигнал лог.1, который выбирает все ЭЗЭ, расположенные в одной из строк матрицы. Если подан сигнал «чтение» (), то информация из выбранных ячеек подается на первые входы выходных элементов 2И. На вторые входы этих ключей подан единичный (пассивный) логический сигнал. Информация, хранившаяся в выбранных ЭЗЭ, попадает на выходные выводы DO0, DO1, DO2, DO3.

Если на схему подан сигнал «запись» (), то информация с входных шин

DO0, DO1, DO2, DO3 через входные элементы 2И подается на входы ЭЗЭ и записывается в них. Особенностью является одновременная запись и считывание информации, хранящейся в строке матрицы ЭЗЭ. Поэтому при заданной разрядности хранимого слова наращивание объема памяти может выполняться только за счет увеличения числа строк матрицы. Это, в свою очередь, ведет к значительному увеличению количества выходов дешифратора, т.е. к усложнению аппаратной реализации.

ROM масочная(дио транзи)

Масочная ROM. На первом этапе формируется заготовка, каждый разряд которой воспроизводится однотипной схемой. На втором этапе, который может быть выполнен только один раз и только на прецизионном оборудовании «лишние» элементы выжигаются с помощью лазерного луча или потока электронов. «Нужные» элементы при этом прикрываются специальным экраном – маской (отсюда и название технологии) Экономически целесообразна для больших тиражей. Основные типы:

диодная,

транзисторная биполярная,

транзисторная полевая;

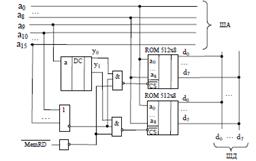

ЗУ (М=16, организация 4х4) с одномерной адресацией. Данная структура содержит матрицу 4х4 ЭЗЭ, каждый из которых снабжен тремя выводами: входом информации (IN)выходом информации (OFF) и входом разрешения работы – выбора кристалла (ES- ciment select), дешифратор адреса, входные и выходные ключи на элементах 2И.

Если на вход дешифратора подано некоторое адресное слово, на соответствующем его выходе формируется сигнал лог.1, который выбирает все ЭЗЭ, расположенные в одной из строк матрицы. Если подан сигнал «чтение» (), то информация из выбранных ячеек подается на первые входы выходных элементов 2И. На вторые входы этих ключей подан единичный (пассивный) логический сигнал. Информация, хранившаяся в выбранных ЭЗЭ, попадает на выходные выводы DO0, DO1, DO2, DO3.

Если на схему подан сигнал «запись» (), то информация с входных шин

DO0, DO1, DO2, DO3 через входные элементы 2И подается на входы ЭЗЭ и записывается в них. Особенностью является одновременная запись и считывание информации, хранящейся в строке матрицы ЭЗЭ. Поэтому при заданной разрядности хранимого слова наращивание объема памяти может выполняться только за счет увеличения числа строк матрицы. Это, в свою очередь, ведет к значительному увеличению количества выходов дешифратора, т.е. к усложнению аппаратной реализации.

ROM масочная(дио транзи)

Масочная ROM. На первом этапе формируется заготовка, каждый разряд которой воспроизводится однотипной схемой. На втором этапе, который может быть выполнен только один раз и только на прецизионном оборудовании «лишние» элементы выжигаются с помощью лазерного луча или потока электронов. «Нужные» элементы при этом прикрываются специальным экраном – маской (отсюда и название технологии) Экономически целесообразна для больших тиражей. Основные типы:

диодная,

транзисторная биполярная,

транзисторная полевая;

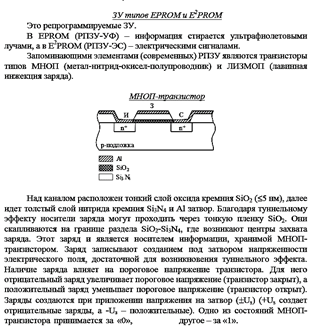

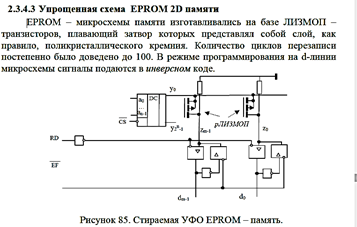

В PROM и EPROM-OTP информация однократно записывается потребителем. Микросхемы PROM программируются пережиганием плавких перемычек программаторов. В исходной заготовке имеются все перемычки, а после программирования остаются только необходимые. Металлические или поликремниевые перемычки в электродах запоминающих элементов расплавляются импульсами тока достаточно большой амплитуды и длительности. В микросхемах памяти на базе многоэмиттерных транзисторов количество эмиттеров соответствует разрядности кодового слова, а количество транзисторов – количеству кодовых слов. Двунаправленный буфер используется для программирования микросхемы. Для этого на адресные входы подаётся двоичное значение, соответствующее номеру выбранной ячейки памяти, на линии данных подаётся записываемое значение, управляющие сигналы устанавливают в следующие значения CS=0, RD=0, EF=0.

В PROM и EPROM-OTP информация однократно записывается потребителем. Микросхемы PROM программируются пережиганием плавких перемычек программаторов. В исходной заготовке имеются все перемычки, а после программирования остаются только необходимые. Металлические или поликремниевые перемычки в электродах запоминающих элементов расплавляются импульсами тока достаточно большой амплитуды и длительности. В микросхемах памяти на базе многоэмиттерных транзисторов количество эмиттеров соответствует разрядности кодового слова, а количество транзисторов – количеству кодовых слов. Двунаправленный буфер используется для программирования микросхемы. Для этого на адресные входы подаётся двоичное значение, соответствующее номеру выбранной ячейки памяти, на линии данных подаётся записываемое значение, управляющие сигналы устанавливают в следующие значения CS=0, RD=0, EF=0.

Strata flash

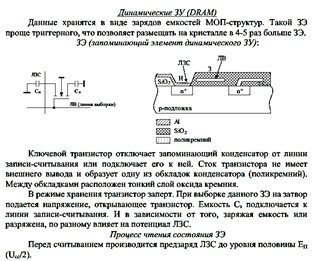

Flash – устройства памяти выполняются на основе технологии EEPROM со следующими особенностями: Стирание ранее записанной информации выполняется поблочно. Сам термин flash и происходит от этой особенности: первоначально используемые устройства для хранения секретной информации автоматически стирали всю матрицу при попытке несанкционированного доступа. Размер блоков варьируется от 256 байт до 128 К. Специальные алгоритмы разравнивания оптимизируют количество перезаписей в разных блоках матрицы.

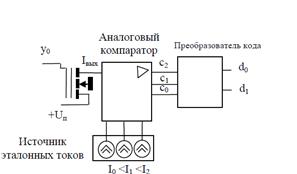

Страта-флэш (strata-flash) устройство памяти характеризуется тем, что один запоминающий элемент способен хранить 2 бита данных и состоит из: двухзатворного ЛИЗМОП – транзистора, аналогового компаратора, выходной комбинационной схемы, преобразующий сигнал в двухразрядное двоичное значение.

Strata flash

Flash – устройства памяти выполняются на основе технологии EEPROM со следующими особенностями: Стирание ранее записанной информации выполняется поблочно. Сам термин flash и происходит от этой особенности: первоначально используемые устройства для хранения секретной информации автоматически стирали всю матрицу при попытке несанкционированного доступа. Размер блоков варьируется от 256 байт до 128 К. Специальные алгоритмы разравнивания оптимизируют количество перезаписей в разных блоках матрицы.

Страта-флэш (strata-flash) устройство памяти характеризуется тем, что один запоминающий элемент способен хранить 2 бита данных и состоит из: двухзатворного ЛИЗМОП – транзистора, аналогового компаратора, выходной комбинационной схемы, преобразующий сигнал в двухразрядное двоичное значение.

Плавающий затвор n-ЛИЗМОП транзистора заряжают одним из 3-х уровней потенциала (четвёртым уровнем является разряженное состояние затвора). От этого зависит степень экранирования потенциала основного затвора (в режиме выбора данного запоминающего элемента h – уровнем на линии y0) и, соответственно, значение тока Iвых. Далее этот ток сравнивается с с тремя эталонными значениями токов и формируются выходные сигналы.

Формирование сигналов

Плавающий затвор n-ЛИЗМОП транзистора заряжают одним из 3-х уровней потенциала (четвёртым уровнем является разряженное состояние затвора). От этого зависит степень экранирования потенциала основного затвора (в режиме выбора данного запоминающего элемента h – уровнем на линии y0) и, соответственно, значение тока Iвых. Далее этот ток сравнивается с с тремя эталонными значениями токов и формируются выходные сигналы.

Формирование сигналов

Устройства памяти с мультиплексированием адресного слова

Устройства памяти с мультиплексированием адресного слова

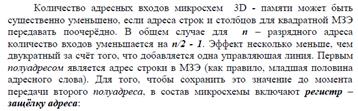

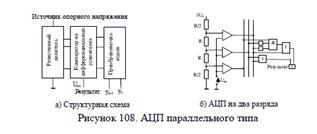

Получаем 16 различных напряжений 2в4

Можно посчитать, что если ключ нулевого разряда установлен в положение " 1", а все остальные в положение " 0", то

Получаем 16 различных напряжений 2в4

Можно посчитать, что если ключ нулевого разряда установлен в положение " 1", а все остальные в положение " 0", то

Uвых=V*1/16,

Uвых=V*1/16,

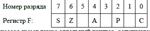

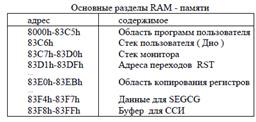

Регистры А, В, С, D, E, H, L образуют группу регистров общего

Регистры А, В, С, D, E, H, L образуют группу регистров общего  назначения (РОН), F- регистр флагов, SP - указатель стека (stack pointer - содержит адрес вершины), а PC - программный счетчик (program counter - содержит адрес следующей выполняемой процессором команды). Регистры SP и PC имеют размер по 16 бит (два машинных слова), поскольку непосредственно используются для адресации памяти.

А - аккумулятор. Как правило, он используется для хранения результата операции и неявно присутствует в качестве операнда некоторых команды.

Особым приемом в работе микропроцессора является использование для хранения информации сразу пары регистров. При этом размер двоичных данных увеличивается до 16 разрядов. Такие пары образуют регистры В и С, D и E. Кроме этого, пара регистров H и L часто используется для косвенной адресации ячейки памяти (т.н. М - ячейка). Регистр F называется флаговым и состоит из разрядов, сохраняющих признаки результата выполненной процессором команды

назначения (РОН), F- регистр флагов, SP - указатель стека (stack pointer - содержит адрес вершины), а PC - программный счетчик (program counter - содержит адрес следующей выполняемой процессором команды). Регистры SP и PC имеют размер по 16 бит (два машинных слова), поскольку непосредственно используются для адресации памяти.

А - аккумулятор. Как правило, он используется для хранения результата операции и неявно присутствует в качестве операнда некоторых команды.

Особым приемом в работе микропроцессора является использование для хранения информации сразу пары регистров. При этом размер двоичных данных увеличивается до 16 разрядов. Такие пары образуют регистры В и С, D и E. Кроме этого, пара регистров H и L часто используется для косвенной адресации ячейки памяти (т.н. М - ячейка). Регистр F называется флаговым и состоит из разрядов, сохраняющих признаки результата выполненной процессором команды  Процессор имеет также отдельный триггер, регулирующий работу процессора с периферийными устройствами, который называется триггер прерываний (ТП). Единичное значение разрешает, а нулевое – запрещает процессору реагировать на сигналы, поступающие на вход INT. Для программного управления этим триггером в составе процессора есть команда EI (установить ТП в 1) и DI (установить ТП в нуль).

В описании команды процессора обычно, кроме выполняемого действия, указывается, какие из флагов данная команда выставляет:

S (signal flag)-флаг знака (0- положительный, 1- отрицательный);

Z (zero flag)- флаг нуля (0- ненулевой, 1- нулевой результат);

А (additional carry)- флаг дополнительного переноса (из третьего в четвёртый разряд);

Р (parity flag)- флаг четности (0- нечетное, 1-четное количество единиц в результате);

С (carry flag)-флаг переноса (из старшего разряда результата);

Пару регистров А и F часто называют регистром PSW (processor status word - слово состояния процессора).

Процессор имеет также отдельный триггер, регулирующий работу процессора с периферийными устройствами, который называется триггер прерываний (ТП). Единичное значение разрешает, а нулевое – запрещает процессору реагировать на сигналы, поступающие на вход INT. Для программного управления этим триггером в составе процессора есть команда EI (установить ТП в 1) и DI (установить ТП в нуль).

В описании команды процессора обычно, кроме выполняемого действия, указывается, какие из флагов данная команда выставляет:

S (signal flag)-флаг знака (0- положительный, 1- отрицательный);

Z (zero flag)- флаг нуля (0- ненулевой, 1- нулевой результат);

А (additional carry)- флаг дополнительного переноса (из третьего в четвёртый разряд);

Р (parity flag)- флаг четности (0- нечетное, 1-четное количество единиц в результате);

С (carry flag)-флаг переноса (из старшего разряда результата);

Пару регистров А и F часто называют регистром PSW (processor status word - слово состояния процессора).

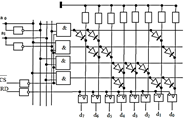

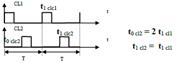

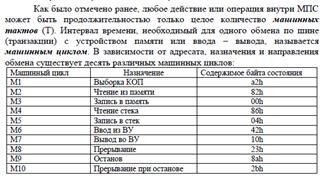

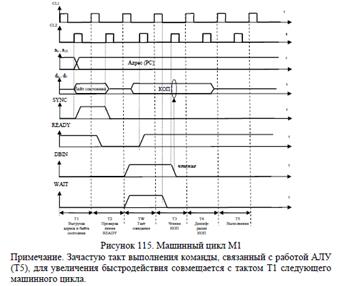

Входные управляющие сигналы (6) * RESET - сигнал сброса. При единичном значении этого сигнала выходные буферы микропроцессора переходят в высокоимпедансное состояние и обнуляется регистр PC. Процессор начинает работу с команды RST0, расположенную по нулевому адресу памяти * CL1 и CL2 - сигналы синхронизации от генератора тактовых импульсов. При одинаковой частоте сигналы имеют разный профиль: По фронту и спаду сигнала CLC2 синхронизируются сигналы «внутри» машинного такта. ГТИ может генерировать также сигнал уменьшенной (в 2 раза относительно рабочей) частоты для тактирования устройств ввода-вывода. * HOLD(удержание) - «захват шин» - запрос на монопольное владение шиной от контроллера (или устройства) ПДП. * INT - запрос аппаратного прерывания. Может быть задействовано 7 запросов, каждый из которых обрабатывается соответствующей командой рестарта RST1-RST7, так как RST0 зарезервирована для начального старта процессора. * READY – готовность (0) информации на ШД к вводу в процессор.

Выходные управляющие сигналы (6): *SYNC - сигнал синхронизации, свидетельствующий о начале каждого машинного цикла. Фактически означает, что на ШД процессором выгружен байт состояния; * WAIT - такт ожидания; *DBIN – (data bus input) приём с шины данных: информация с ШД принимается процессором; * WR – запись: процессором на ШД выгружена информация, предназначенная для записи в память или внешнее устройство; *INTE - подтверждение запроса прерывания; * HLDA (hold acknowledge - признать удержание)– подтверждение запроса «захват шин».

Выходные линии шины адреса (а0 - а15).

Двунаправленные линии шины данных (d0 – d7).

Команды, ржимы адресациипамяти Режимами адресации памяти называют способы задания операндов в командах процессора: * Регистровая адресация – наиболее простой вид адресации. В команде указывается имя регистра, содержимое которого является операндом команды;

MOV A, B *Непосредственная адресация – операндом команды является число, используемое в качестве источника данных. Допускается число записывать в различных системах счисления (без суффикса – десятичное, с суффиксом “h” – шестнадцатеричное, с суффиксом “b” - двоичное);

MVI A, 12h *Регистровая косвенная – содержимое пары регистров (в команде указывается первый из регистров пары) используется, как адрес ячейки памяти. LDAX B; A< - [BC] Разновидностью косвенной регистровой адресации является технология использования т.н. М-ячейки. Так в общем случае называется байт адресуемого пространства памяти, адрес которого в данный момент содержится в паре регистров HL; MOV M, A [HL] < - A *Прямая адресация – в команде указывается адрес ячейки памяти (или порта ввода – вывода), содержимое которой является операндом;

LDA 800h; A < - [800h]

Входные управляющие сигналы (6) * RESET - сигнал сброса. При единичном значении этого сигнала выходные буферы микропроцессора переходят в высокоимпедансное состояние и обнуляется регистр PC. Процессор начинает работу с команды RST0, расположенную по нулевому адресу памяти * CL1 и CL2 - сигналы синхронизации от генератора тактовых импульсов. При одинаковой частоте сигналы имеют разный профиль: По фронту и спаду сигнала CLC2 синхронизируются сигналы «внутри» машинного такта. ГТИ может генерировать также сигнал уменьшенной (в 2 раза относительно рабочей) частоты для тактирования устройств ввода-вывода. * HOLD(удержание) - «захват шин» - запрос на монопольное владение шиной от контроллера (или устройства) ПДП. * INT - запрос аппаратного прерывания. Может быть задействовано 7 запросов, каждый из которых обрабатывается соответствующей командой рестарта RST1-RST7, так как RST0 зарезервирована для начального старта процессора. * READY – готовность (0) информации на ШД к вводу в процессор.

Выходные управляющие сигналы (6): *SYNC - сигнал синхронизации, свидетельствующий о начале каждого машинного цикла. Фактически означает, что на ШД процессором выгружен байт состояния; * WAIT - такт ожидания; *DBIN – (data bus input) приём с шины данных: информация с ШД принимается процессором; * WR – запись: процессором на ШД выгружена информация, предназначенная для записи в память или внешнее устройство; *INTE - подтверждение запроса прерывания; * HLDA (hold acknowledge - признать удержание)– подтверждение запроса «захват шин».

Выходные линии шины адреса (а0 - а15).

Двунаправленные линии шины данных (d0 – d7).

Команды, ржимы адресациипамяти Режимами адресации памяти называют способы задания операндов в командах процессора: * Регистровая адресация – наиболее простой вид адресации. В команде указывается имя регистра, содержимое которого является операндом команды;

MOV A, B *Непосредственная адресация – операндом команды является число, используемое в качестве источника данных. Допускается число записывать в различных системах счисления (без суффикса – десятичное, с суффиксом “h” – шестнадцатеричное, с суффиксом “b” - двоичное);

MVI A, 12h *Регистровая косвенная – содержимое пары регистров (в команде указывается первый из регистров пары) используется, как адрес ячейки памяти. LDAX B; A< - [BC] Разновидностью косвенной регистровой адресации является технология использования т.н. М-ячейки. Так в общем случае называется байт адресуемого пространства памяти, адрес которого в данный момент содержится в паре регистров HL; MOV M, A [HL] < - A *Прямая адресация – в команде указывается адрес ячейки памяти (или порта ввода – вывода), содержимое которой является операндом;

LDA 800h; A < - [800h]

Примечание:

1. Если команда однобайтная и безоперандная (или операнды – регистры), в машинном цикле М1 осуществляется и выполнение команды;

2. Цикл М2 следует за М1 для загрузки второго и третьего байта команды, а также операнда(ов) из памяти;

3. Тип машинного цикла идентифицируется байтом состояния, который формируется процессором и передаётся шинному формирователю в такте Т1.

Командным циклом называется набор машинных циклов, необходимый для выполнения одной команды. Как было указано ранее, для однобайтных безоперандных команд и однобайтных команд с регистровой адресацией командный цикл совпадает с машинным циклом М1. Для команды, например

На диаграмме, представленной ниже, воспроизведены сигналы для машинного цикла М1 – выборки и исполнения команды. Машинный такт синхронизируется передним фронтом CL1, а начало микрооперации (действие внутри машинного цикла), как правило, - фронтом CL2.

Примечание:

1. Если команда однобайтная и безоперандная (или операнды – регистры), в машинном цикле М1 осуществляется и выполнение команды;

2. Цикл М2 следует за М1 для загрузки второго и третьего байта команды, а также операнда(ов) из памяти;

3. Тип машинного цикла идентифицируется байтом состояния, который формируется процессором и передаётся шинному формирователю в такте Т1.

Командным циклом называется набор машинных циклов, необходимый для выполнения одной команды. Как было указано ранее, для однобайтных безоперандных команд и однобайтных команд с регистровой адресацией командный цикл совпадает с машинным циклом М1. Для команды, например

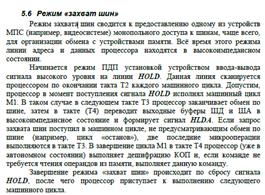

На диаграмме, представленной ниже, воспроизведены сигналы для машинного цикла М1 – выборки и исполнения команды. Машинный такт синхронизируется передним фронтом CL1, а начало микрооперации (действие внутри машинного цикла), как правило, - фронтом CL2.  Кроме работы под управлением потока команд соответствующей программы, МПС может находиться в одном из особых режимов работы: Прерывание; Захват шин; Останов; Прерывание при останове

Кроме работы под управлением потока команд соответствующей программы, МПС может находиться в одном из особых режимов работы: Прерывание; Захват шин; Останов; Прерывание при останове