Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Арифметические и логические команды

|

|

Все рассмотренные выше команды были либо командами переходов, либо командами пересылки информации. Обратимся теперь к командам обработки информации. К ним относятся команды сложения, вычитания, логического И, логического ИЛИ, команды сдвигом и т. д. В качестве типичного представителя этого класса рассмотрим «сложение с- регистром и переносом» ADC R.

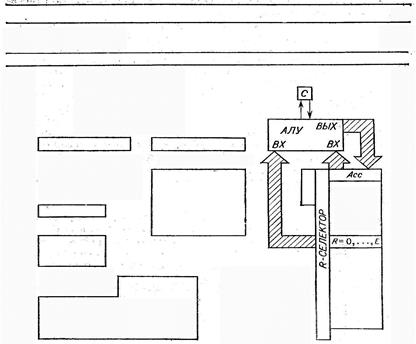

На рис. 4.13 показаны потоки информации, когда R задает любой общий регистр в диапазоне 016,..., Е16. В соответствии с табл. 4.2 это однобайтовая команда. Следовательно, после второго синхроимпульса первого и единственного машинного цикла содержимое аккумулятора и регистра R может быть подано на входы АЛУ в качестве операндов. АЛУ по этим двум операндам и переносу С (считая его переносом в младший разряд) вычисляет 8-разрядную сумму и новое значение переноса.

Рис. 4.13 Информационные потоки в фазе выполнения команды ADC R, когда R ¹ 11112

Таким образом, по третьему синхроимпульсу машинного цикла сумма передается в аккумулятор, а результирующий перенос — в триггер переноса С.

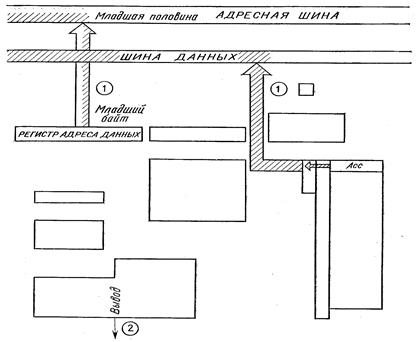

Выполнение команды ADC R при R = 11112 показано на рис. 4.14.

Рис. 4.14 Информационные потоки в фазе выполнения команды

ADC R, когда R = 11112

В этом случае второй машинный цикл затрачивается на выборку операнда из памяти по адресу на регистрах Н и L. Этот операнд временно заносится в младшие разряды регистра адреса данных и оттуда через R-селектор в нужный момент подается на вход АЛ У.

Команды ввода/вывода

Теперь рассмотрим группу команд, обеспечивающих передачу информации между микропроцессором и устройствами ввода/вывода. Для конкретности остановимся на команде OUT. Поскольку это двух байтовая команда, второй байт во втором машинном цикле будет помещен в регистр адреса данных в младшую его половину. В связи с задержками распространения сигнала в шинах, а также в логических схемах устройств вывода и самого микропроцессора в фазе выполнения команды используется третий машинный цикл.

Этот цикл иллюстрирует рис. 4.15

Рис. 4.15 Информационные потоки в фазе выполнения команды OUT

По первому синхроимпульсу третьего машинного цикла содержимое младшей половины регистра адреса данных подается на адресную шину, а содержимое аккумулятора через г-селектор — на шину данных. Все устройства вывода декодируют содержимое младшей половины адресной шины. Однако только то устройство, которое опознает код на адресной шине как свой код, подает разрешающий сигнал на прием информации с шины данных в свой входной регистр. По второму синхроимпульсу третьего машинного цикла БУС подаст сигнал на линию «вывод» шины управления, который стробирует передачу содержимого шины данных в открытый для приема регистр.

|

|