Преобразователи кодов и арифметические устройства.

Реальные последовательностные автоматы обязательно содержат в своём составе комбинационную часть – АЛУ (см. рис.5.8)., которое производит арифметическое и логическое преобразование информации в соответствии с заданной программой. Проектирование АЛУ опирается на типовые решения отдельных узлов, выполняющих логические и арифметические действия.

Простейшие логические ячейки, применяемые в АЛУ, описаны ранее (см. вопрос 5.3, 5.4). Рассмотрим схемы узлов, через которые информация подаётся с вводных устройств на регистры УФС для дальнейшего преобразования или посредством которых преобразуется информация, снимаемая с выходных регистров УФС для подачи на входы автомата. Такие узлы называются преобразователями кодов. В вопросе 5.4 уже рассмотрена схема преобразователя кода Грея, получаемого от кодового датчика положения. В арифметический двоичный код, удобный для обработки в УВМ. Здесь мы рассмотрим схемы дешифраторов, которые преобразуют двоичный код выходных регистров УВМ в единичный сигнал на одном из выходов, номер которого задаётся кодом, поступающим на дешифратор. Иными словами, дешифратор определяет номер выхода, на который необходимо подать единичный сигнал. Поэтому дешифратор называют преобразователем двоичного кода в единичный.

Поскольку конъюнкция равна единице только на одном наборе логических переменных, то простейший дешифратор есть совокупность схем, реализующих логическое умножение заданных кодовых сигналов. Такой дешифратор называется линейным. Схема линейного дешифратора и его условное обозначение приведены на рис.5.17.

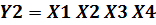

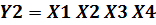

Нет необходимости анализировать таблицу истинности линейного дешифратора, чтобы получить схему, представленную на рис.5.17, так как его логические выражения могут быть получены непосредственно из заданных условий функционирования и не поддаются минимизации. Например, логическая функция выхода Y2 (см. рис.5.17) может быть непосредственно выражена в виде:

. .

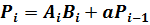

В качестве примера комбинационных арифметических устройств рассмотрим схему суммирования двоичных чисел. Каждый i -й разряд такой схемы должен обеспечить показ единицы в трёх случаях:

1) когда имеется перенос из младшего разряда, а слагаемые равны нулю (Pi-1 = 1; Ai = 0 и Bi = 0);

2) когда одно из слагаемых равно единице (Ai = 1 или Bi = 1), а другое слагаемое равно нулю и нет переноса из младшего разряда (Pi-1 = 0);

3) когда оба слагаемых равны единице и имеется перенос из младшего разряда (Ai = 1, Bi = 1 и Pi-1 = 1).

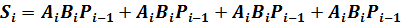

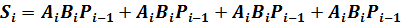

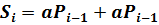

В остальных случаях содержимое i-го разряда сумматора должно быть равно нулю. Очевидно, что этим условиям соответствует логическая формула:

, (5.13) , (5.13)

где Si – значение i -го разряда сумматора.

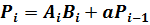

Помимо формирования собственного значения каждый разряд (ячейка) сумматора должен формировать сигналы переноса в следующий (i+1) -й разряд. Условиями переноса в следующий разряд являются:

1) равенство единице обоих слагаемых одновременно (Ai = 1 и Bi = 1) независимо от значения Pi-1;

2) равенство единице одного из слагаемых и сигнала переноса из младшего разряда (Ai = 1 или Bi = 1 и одновременно Pi-1 = 1) независимо от значения другого слагаемого.

Исходя из этих условий, получаем следующую формулу для сигнала переноса Pi:

. (5.14) . (5.14)

Схема ячейки сумматора, реализованная непосредственно по формулам (5.13), (5.14) в базисе И-НЕ, приведена на рис.5.18.

Рис.5.18. Схема ячейки сумматора (а) и её условное обозначение (б).

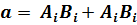

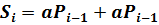

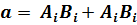

Если употребить скобочные формы формул (5.13) и (5.14):

; ;

; (5.15) ; (5.15)

, ,

где функция a получена вынесением за скобки в формуле (5.13), то ячейку сумматора можно построить на однотипных двухпроводных логических схемах И-НЕ. Реализация ячейки сумматора будет проще, но быстродействие её уменьшится в 2 раза, так как формирующиеся сигналы должны будут проходить через промежуточные цепи, реализующие функцию a. Условное обозначение, приведённое на рис.5.18, б, предполагает, что инверсные значения Ai, Bi и Pi-1 формируются внутри ячейки сумматора.

Схема сумматора, составленного из ячеек, представленных на рис.5.18, б, приведена на рис.5.19.

Рис.5.19. Схема четырёхразрядного комбинационного сумматора.

Поскольку перенос в самый младший разряд сумматора не реален, то его вход переноса соединяется с общей точкой, что соответствует нулевому значению сигнала переноса. Данный сумматор является комбинационной схемой, поэтому полученная сумма должна быть зафиксирована в каком-либо регистре, например, в аккумуляторе микропроцессора, управляющего вычислениями.

Сумматоры применяются и для выполнения операций вычитания (сложения отрицательных чисел), для чего последние должны быть представлены в дополнительном коде (см. вопрос 2.4.2). Операции умножения и деления выполняются, как показано ранее, с помощью операций сдвига, на регистрах.

Богатый выбор типовых решений как последовательностных, так и комбинационных устройств различного назначения приводит к тому, что при анализе и синтезе сложных последовательностных автоматов, таких как БИС микропроцессорных устройств управления, опираются именно на эти решения, а не на всеобъемлющий анализ состояний автомата. Кроме того, сложные управляющие устройства характеризуются миллионами состояний, полностью рассмотреть которые без декомпозиции, т.е. разделения устройства на составляющие блоки, находящиеся в иерархической зависимости друг от друга, очень затруднительно даже методами машинного анализа.

При анализе управляющих устройств АСУТП мы будем, как и ранее, последовательно производить их декомпозицию с учётом иерархической структуры АСУТП, а составлять управляющие программы будем, опираясь на иерархию управленческих решений.

|

.

. , (5.13)

, (5.13) . (5.14)

. (5.14) ;

; ; (5.15)

; (5.15) ,

,