Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Организацияпамятипервогоуровня

|

|

Основное назначение памяти первого уровня (СОП) - повысить быстродействие памяти ЭВМ и, следовательно, быстродействие ЦП. Действительно, время выполнения команды определяется суммой:

Тком = τ ком + n τ опер + τ вып + τ рез

и, как видно из этого выражения, существенно зависит от времени обращения к памяти ЭВМ. Время выполнения команды можно существенно уменьшить, если сократить время обращения к памяти. Как?

1) Увеличивая быстродействие основной памяти (это дорого и непросто); 2) Между ОП и ЦП поставить СОП в качестве буфера (рис. 2).

| управление |

| ОП |

| команды |

| данные |

| СОП |

В РОН программист размещает часто используемые данные, обращение к которым осуществляется быстрее (в 3 - 5 раз), чем к ячейкам ОП. В результате команды, которые оперируют данными из РОН, выполняются быстрее. Пример: команды типа регистррегистр RR, регистр-память RS выполняются быстрее, чем команды типа память-память SS. Конструктивно (буфер)

Рис .2

РОН обычно располагают на одном кристалле (плате) вместе с ЦП (рис. 4).

Второй вариант организации буфера - буфер, недоступный, скрытый от программиста –Cache Memory (КЭШ). Кэш-буфер и используется как для хранения команд, так и для хранения данных. Емкость кэш-буфера - десятки, сотни КВ. ”Скрытость” кэш-буфера обеспечивает специальный механизм, который реализует автоматический (аппаратноуправляемый) обмен между ОП и буфером. Единицей обмена обычно является более крупная, чем слово, величина - т.е. строка кэша длиной в несколько слов. Более крупная единица обмена сокращает частоту обменов с ОП. В случае пословного обмена каждое слово в ОП, к которому обращается ЦП, размещается (дублируется) в соответствующей ячейке СОП. В случае более крупной единицы обмена в кэш дублируется целиком тот блок информации, к отдельному слову которого обращается ЦП. При этом существует большая вероятность, что последующие обращения со стороны ЦП будут к соседним словам этого блока и, следовательно, будут обслуживаться кэш-памятью без дополнительных обращений к ОП. команды

| ЦП |

| ОП |

| Буфер |

| ( |

| РОН |

| ) |

| данные |

| ком |

| . |

| данн |

| . |

| ЦП |

| данн |

| ОП |

| РОН |

| КЭШ |

| данн |

| . |

| ком |

| . |

Рис. 3

Рис. 4

Следует отметить, что буфер данных типа РОН организуется на основе ЗУсадреснойорганизацией.

Скрытый буфер (кэш) команд и данных организуется на основе ЗУсбезадреснойорганизацией, в частности, на основе ЗУ с ассоциативной организацией.

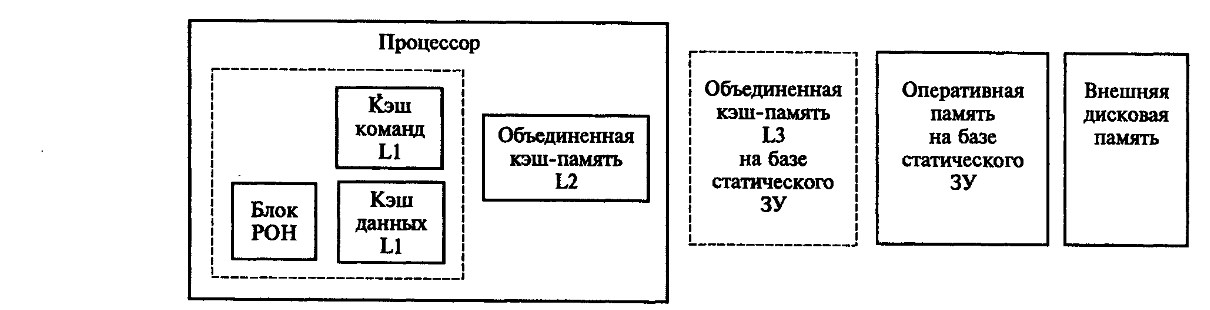

Обычно все содержимое кэш L1 находится в кэш L2, а все содержимое кэш L2 является частью кэш L3. Принципы построения кэш-памяти всех уровней сходны. В целом ОП вместе с кэшами всех уровней представляет собой единую систему памяти, непосредственно доступную процессору для чтения и записи данных, а также считывания команд программы.

Емкостьпамяти 200 байт 16...32 256...512 Кбайт 1...4 Мбайт 64...256 Мбайт 8...64 Гбайт

Кбайт

Времядоступа 5 нс < 10 нс < 10 нс < 10 нс 30...60 н c 5...30 мс

Рис. 5. СтруктурапамятисовременныхВМ:

РОН — регистрыобщегоназначения; Li, L2, L3 — уровникэш - памяти;

ОЗУ — оперативноезапоминающееустройство;

DRAM - сверхбольшиеинтегральныесхемысдинамическойпамятью

Внешняя кэш-память второго уровня процессоров Pentium Pro, Pentium ll/lll, Xeon и Athlon компании AMD содержит дополнительно соответственно 15, 5 (256 Кбайт), 31 (512 Кбайт), 62 (1 Мбайт) и 124 млн (2 Мбайт) транзисторов в отдельных микросхемах. Внешняя кэш-память третьего уровня объемом 2 или 4 Мбайт, включенная в процессор Itanium, содержит уже около 300 млн транзисторов. Различные версии процессора Athlon могут содержать кэш-память второго уровня, расположенную на отдельной микросхеме и работающую на частоте, равной половине, двум пятым или одной трети частоты ядра, либо встроенную кэш-память меньшего объема, частота которой равняется частоте ядра.

|

|