Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Структура контролера

|

|

Структурно контролер складається з двох основних частин: ядра та факультативної частини (рис. 3.3).

Рис. 3.3. Структура контролера (ДК – дискретні канали, АК – аналогові канали, ЛК – лінії керування)

До складу ядра входить мінімальна добірка великих інтегральних схем (ВІС) мікропроцесорного комплекту, необхідних для виконання задач керування. Зокрема, ядро повинно вміщувати:

- Мікропроцесор К1821ВМ85А;

- ВІС оперативного запам’ятовуючого пристрою (ОЗП) з організацією 2К слів х 8 розрядів;

- ВІС постійного запам’ятовуючого пристрою (ПЗП) з організацією 1К слів х 8 розрядів;

- програмований таймер;

- контролер переривань;

- ВІС послідовного інтерфейсу так, як типу інтерфейсу зв’язку з ПЕОМ-RS232C;

- контролер прямого доступу до пам’яті.

Факультативна частина контролера вміщує додаткові об’єми ОЗП та периферійних ВІС, необхідних для роботи з заданим у варіанті об’єктом керування і визначається характеристиками останнього.

Факультативна частина реалізує цифрові та аналогові канали вводу-виводу інформації, за допомогою яких контролер взаємодіє з об’єктом керування.

Канали аналогового вводу-виводу реалізуються на підставі відповідних схем АЦП або ЦАП і схем аналогових мультиплексорів-демультиплексорів, які забезпечують необхідну кількість аналогових каналів.

4. Описи функціональної та принципової схеми контролера.

До складу мікропроцесорної системи входять компоненти. Що приведені у попередньому розділі. В поточному розділі розглянемо схеми включення усіх компонентів в одну загальну систему.

4.1 Побудова ядра МПС

Для нормальної роботи побудуємо три шини: адреси, даних та керування.

Тому що шина даних й адреси в мікропроцесора К1821ВМ85 сполучені й мають поділ тільки в часі, то для їхнього поділу будемо використати регістри із третім станом К580ИР82 для зберігання адреси, і шинні формувачі К580ВА86 для передачі даних по шині даних.

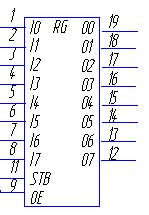

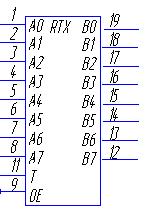

Умовне графічне позначення мікросхеми К580ИР82 показане на рисунку 3.1, а К580ВА86- на рисунку 3.2.

Рисунок 3.1 Умовне графічне позначення К580ИР82

Рисунок 3.4 Умовне графічне позначення К580ВА86

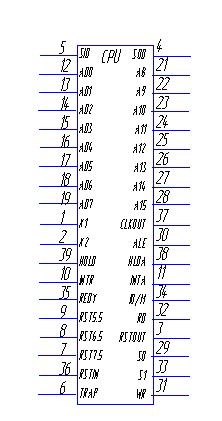

Мікропроцесор К1821ВМ85- це однокристальний восьми розрядний процесор з фіксованим набором команд.Він має класичну архітектуру з одним акумулятором и відділеними шинами адреси і даних.

Мікропроцесор має наступні характеристики:

- напруга живлення +5В

- споживча потужність 0.2Вт

- тактова частота 5МГц

- тривалість виконання операції додавання типу «регістр-регістр» 0.8 мкс

- навантажувальна здатність – один вихід ТТЛ- схеми

- може обслуговувати 256 пристроїв вводу та виводу

- виходи напруг Uol < 0.4B; Uoh> 3.7 B;

- число команд – 80

- адресний простір пам’яті – 64 Кбайт

Умовне графічне позначення мікропроцесора показано на рисунку 3.1

Рисунок 3.3 умовне графічне позначення мікропроцесора К1821ВМ85

Функціонування мікропроцесора в часі визначається внутришним генератором тактових імпульсів. Його взбудження може задаватися зовнішнім кварцовим резонатором, RC- або LC- ланцюгами, а також зовнішнім генератором, які підключаються до входів Х1, Х2 мікропроцесора (дивись рисунок 3.2)

Вибираємо схему синхронізації з кварцовим резонатором який вибирається на чистоту 5МГц. Конденсатор призначений для подавлення інших гармонік на частоті 5МГц і вибирається ємністю 20 пФ.

З довідника / / вибираємо тип конденсатора КМ-5б-М470-20 пФ.

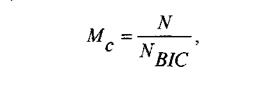

В зв’язку з тим, що шина адреси має 16 розрядів, а одна мікросхема К580ИР82 має 8 розрядів розраховуємо необхідну кількість мікросхем за формулою 3.1

(3.1)

де Мс- кількисть мікросхем

N- кількість розрядів шини адреси

NBic- кількість розрядів в одній мікросхемі

Mc=16/8=2

В зв’язку з тим що шина даних в МПС має 8 розрядів, то необхідно використовувати одну мікросхему К580ВА86.

ОЗУ необхідно для зберігання різних проміжних даних і результатів розрахунку. ОЗУ виконано на мікросхемі К537РУ8А. Ця мікросхема має ємність 2К, розрядність слова 8 біт. Для організації 8 розрядної шини даних необхідно паралельне включення двох таких мікросхем. Розрахунок ємності пам'яті буде наведений нижче. На малюнку 3.6 наведене умовне графічне позначення.

Рисунок 2.6 – Условное графическое обозначение К537РУ8А

Дана мікросхема має 3х імпендансний стан виходів, а також вхід дозволу читання або запису в мікросхему. Для керування даною мікросхемою на читання або запис будемо використовувати логічний ланцюг, що приведений на рисунку 2.7.

Рисунок 2.7 – Керування ОЗП.

ПЗП даної МП системи побудований на мікросхемі КР556РТ17, що має 9и розрядний адресний вхід и восьми розрядне вихідне слово. Згідно завдання ПЗП повинно мати ємність 1К байт. На рисунку 2.8 приведено умовне графічне позначення КР556РТ5.

Рисунок 2.8 – Умовне графічне позначення КР556РТ17

В зв’язку з тим, що ПЗП має ємність 1Кх8, а одна мікросхем-512х8, то беремо дві мікросхеми.

В якості послідовного інтерфейсу для зв’язку з RS232 використовуємо адаптер послідовного інтерфейсу К580ВВ51А. На рисунке 2.13 приведено умовне графічне позначення К580ВВ51А.

Рисунок 2.12 – Умовне графічне позначення К580ВВ51А

Це універсальний синхронно-асинхронний прийомо-передаючий пристрій. Крім перетворення форми інформації виконуються функції контролю і керування. До складу мікросхеми входять: передавач, схеми керування модемом, приймача та блока спряження адаптера з системною шиною МП.

Програмовний таймер КР580ВИ53 призначений для організації роботи МП систем і формування сигналів з різними часовими та частотними характеристиками. Умовне позначення показано мікросхеми на рисунку 5.42.

Рис 6.42. Умовне позначення КР580ВИ53

Призначення виходів:

CLK0 - CLK2 - входи тактових імпульсів;

GATE0 - GATE2 - входи дозволу лічення;

OUT0 - OUT2 – виходи лічильника

Схема таймера містить: блок керування читанням/записом RWCU з регістром керувального слова RCW, тристабільний буфер даних BD, три канали на базі 16-розрядних від'ємних лічильників CТ0-CT2. Кожний канал містить лічильник, вхідні та вихідні буферні регістри. Лічильники можуть працювати у двійковому або двійково-десятковому коді. Максимальна частота лічильника становить 2 МГц для КР580ВИ53.

Контролер прямого доступу до пам'яті КР580ВТ57 призначений для організації швидкісного обміну даними між пам'яттю і зовнішніми пристроями, який ініціюється зовнішнім пристроєм.

Кожний з чотирьох каналів ПДП забезпечує передачу блоку даних ємністю до 16 кбайт з довільною початковою адресою в діапазоні 0-64 кбайт. Пріоритети каналів можуть бути фіксованими (канал 0 має найвищий пріоритет, канал 3 - найнижчий) або змінюватися циклічно. В останньому випадку каналу, у якому відбулося обслуговування запиту ПДП, присвоюється нижчий пріоритет, а каналу з наступним номером - вищий.

Молодший байт адреси пам'яті видається по лініях A3-A0 та А7-А4, які безпосередньо підключені до шини адреси АВ. Старший байт адреси передається через шину D7-D0, тому в схему підключено буферний регістр К589ИР12, який фіксує значення старшого байта по сигналу ADSTB при AEN = 0. На вивід CS ВІС надходить сигнал з виходу дешифратора адрес уведення-виведення. Інші виводи КПДП приєднуються до однойменних ліній шин МП системи.

Програмовими контролер переривань КР580ВН59А являє собою пристрій, що реалізує в МПС обробку запитів переривань від зовнішніх пристроїв, як-то датчиків аварійних ситуацій або ПВВ, що реалізують протокол обміну за перериванням.

ВІС ПКП виконує такі функції:

- запам'ятовує запити переривання, які задаються переднім фронтом

або потенціалом;

- маскує, тобто забороняє виконання обраних запитів;

- формує вектор переривання та виконує дії по переходу на підпрог

раму обробки запиту;

- формує сигнал переривання для МП;

- виконує пріоритетну обробку запитів переривання.

Одна ВІС ПКП обробляє вісім запитів на переривання, але за каскадного вмикання кількох ВІС кількість запитів переривання може бути збільшена до 64.

4.2 Побудова факультативної частини МПС

До факультативної частини входять:

- пристрій введення інформації від пристрою вводу графічної інформації;

- пристрій виведення інформації на реєструючий пристрій;

- додаткова пам'ять для зберігання масиву даних.

Пристрій введення інформації містить в своєму складі два 12-розрядних аналого-цифрових перетворювачів (на кожну координату окремо) та паралельний інтерфейс.

В якості паралельного інтерфейсу використовуємо мікросхему К580ВВ55. На рисунку 2.12 приведено умовне графічне позначення К580ВВ55.

Рисунок 2.12 – Умовне графічне позначення К580ВВ55.

Для спряження із зовнішніми пристроями мікросхема має дві групи А и В (по 12 розрядів). Інтерфейс складається із схем керування вводом-виводом, буфера шини даних, схеми керування групами А и В и трьох 8 розрядних портів А, В і С, причому порт С складається из двух 4х розрядних портів, що програмуються окремо. Інтерфейс буде працювати в 0 режимі.

В 0-му режимі будуть працювати вся групи. Причому входи групи А під’єднуємо до виходів першого АЦП, а входи групи В- до виходів другого АЦП.

В якості АЦП використовуємо мікросхему MAX175. Це 12- розрядний швидкісний АЦП послідовного приближення, що працює з ТТЛ–рівнями. Ця мікросхема в своєму складі містить блок цифрового керування, тому цей пристрій, можна, підключати без шинних формувачів спряження. На рисунку 2.9 приведено умовне графічне позначення MAX175.

Рисунок 2.9 – Умовне графічне позначення MAX175.

Пристрій виведення інформації містить в своєму складі паралельний інтерфейс, який буде працювати в 0 режимі та два 12-розрядних цифро - аналогових перетворювачів (на кожну координату окремо).

Виходи групи А паралельного інтерфейсу під’єднуємо до входів першого ЦАП, а виходи групи В- до другого.

4.3 Розробка схеми адресації пристроїв вводу-виводу

Розподіл адресного простору вводу – виводу між існуючим в МПС інтерфейсами та пристроями вводу – виводу показаний в таблиці 4.1.

Таблиця 4.1 - Розподіл адресного простору вводу – виводу

| А7 | А6 | А5 | А4 | А3 | А2 | А1 | А0 | Пристрої вводу - виводу |

| Дані послідовного інтерфейсу | ||||||||

| Керуюче слово послідовного інтерфейсу | ||||||||

| Порт А ППІ1 | ||||||||

| Порт В ППІ1 | ||||||||

| Порт С ППІ1 | ||||||||

| Керуюче слово ППІ1 | ||||||||

| Порт А ППІ2 | ||||||||

| Порт В ППІ2 | ||||||||

| Порт С ППІ2 | ||||||||

| Керуюче слово ППІ2 | ||||||||

| Таймер СТ0 | ||||||||

| СТ1 | ||||||||

| СТ2 | ||||||||

| Керуюче слово | ||||||||

| Контролер переривань | ||||||||

| Контролер переривань | ||||||||

| Х | Х | Х | Х | Адреси контролера прямого доступу до пам’яті |

5. Розробка програми.

|

|