Главная страница Случайная страница

Разделы сайта

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

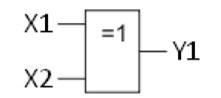

Исключительное ИЛИ

|

|

Этот логический элемент имеет необычный смысл работы: на выходе появится логический уровень в том случае, если только на одном из входов будет присутствовать логическая единица. Если на оба входа (или на все) подать одинаковые уровни, тогда на выходе уровень не изменится.

20 Классификация триггеров и условное обозначение информационных и вспомогательных входов триггеров.

Триггер – это простейшее последовательностное устройство, которое обладает двумя устойчивыми состояниями. В микроэлектронном исполнении выпускают триггеры, различающиеся по сложности построения, по своим функциональным возможностям, по способу управления. Входы, как и сигналы, подаваемые на них, делятся на информационные и вспомогательные. Информационные сигналы через соответствующие входы управляют состоянием триггера. Сигналы на вспомогательных входах служат для предварительной установки триггера в заданное состояние и его синхронизации. Вспомогательные входы могут при необходимости выполнять роль информационных.

Входы и выходы триггеров, как и соответствующим им, сигналы, принято обозначать буквами S, R, D, Q, J и др.

Триггеры классифицируют по ряду признаков. По функциональным возможностям выделяют:

а) триггер с раздельной установкой 0 и 1 (RS-триггер);

б) триггер с (приемом информации по данному входу (D-триггер) другое название: триггер задержки;

в) триггер со счетным входом (Т-триггер);

г) универсальный триггер (JК-триггер).

По способу приема информации триггеры подразделяют на асинхронные (нетактируемые) и синхронные (тактируемые). Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входах триггера. Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специально предусматриваемом входе С. Синхронные триггеры подразделяют на триггеры со статическим управлением по С-входу и с динамическим управлением Tpиггepы со статическим управлением реагируют на информационные сигналы при подаче на вход С уровня 1 (прямой С-вход) или 0 (инверсный C-вход).

Триггеры с динамическим управлением реагируют на информационные сигналы в момент изменения сигнала на C-входе от 0 К 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые. Одноступенчатые триггеры имеют одну ступень запоминания информации. Запись информации в такие триггеры представляет собой непрерывный во времени процесс установления состояния триггера под воздействием информационных сигналов.

Двухступенчатые триггеры имеют две ступени запоминания информации, которые тактовым импульсом управляются таким образом, что в начале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе триггера.

21 RS-триггеры. Схема, работа, таблица состояний, диаграммы работы.

Триггер – это электронное устройство, которое предназначается для записи и хранения информации. Обычно он имеет два выхода: прямой и инверсный; и некоторое количество входов, в зависимости от выполняемой задачи. Под действием входных сигналов, изменяется состояние выходов. Напряжение на выходах изменяется резко – скачкообразно. Для изготовления триггеров обычно используются биполярные, униполярные транзисторы (полупроводниковые приборы).

Информация может записываться в триггеры свободно (непрерывно), то есть при подаче сигналов на вход, состояние выхода меняется в реальном времени. Такие триггеры называются асинхронными. А может информация записываться, только когда активен синхронизирующий сигнал. При отсутствии положительного уровня напряжении на нем, информация на выходах измениться не может – синхронные (тактируемые) триггеры.

RS-триггер именуется так из-за названия его входов:

R – reset (сбросить);

S– set (установить).

Он оснащен двумя входами, как говорилось, и двумя выходами:

Q – прямой выход;

– инверсный.

– инверсный.

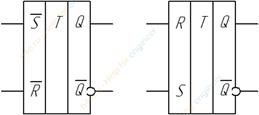

Асинхронный RS-триггер можно реализовать на логических элементах двумя схемами:

- 2 " ИЛИ-НЕ";

- 2 " И-НЕ".

*Синий провод – «0», красный – «1»

Рисунок 1 – Схема асинхронного RS-триггера на логических «2ИЛИ-НЕ» элементах

Первая схема реализована на двух логических ИЛИ-НЕ, по рисунку 1 рассмотрим принцип работы приведенного RS-триггера. В нулевой момент времени, когда ни на один вход (R и S) не подана логическая единица, прямой выход Q=0, соответственно, инверсный  =1. Если на вход S подать напряжение, уровень которого будет соответствовать единице, то выход Q скачкообразно изменит свое значение на 1, а

=1. Если на вход S подать напряжение, уровень которого будет соответствовать единице, то выход Q скачкообразно изменит свое значение на 1, а  на 0. Это произойдет запись информации. Если убрать единицу с “Set”, тогда выходы не изменят свое состояние, останутся такими, какими были – проявление свойства памяти. При подаче положительного сигнала на вход сброса, то есть R=1, инверсный выход резко станет равен 1, а прямой Q – 0. В работе RS-триггера есть недостаток: существует запрещенная комбинация. Нельзя одновременно подавать единичные сигналы на оба входа, нормальная работа триггера в этом случае невозможна.

на 0. Это произойдет запись информации. Если убрать единицу с “Set”, тогда выходы не изменят свое состояние, останутся такими, какими были – проявление свойства памяти. При подаче положительного сигнала на вход сброса, то есть R=1, инверсный выход резко станет равен 1, а прямой Q – 0. В работе RS-триггера есть недостаток: существует запрещенная комбинация. Нельзя одновременно подавать единичные сигналы на оба входа, нормальная работа триггера в этом случае невозможна.

Рисунок 2 - Схема асинхронного RS-триггера на логических «2И-НЕ» элементах

Вторая схема собрана с помощью двух логических элементов И-НЕ. Разница между ними заключается в том, что управление в прошлой схеме осуществлялось положительным сигналом (единицей), а в текущей активный уровень – ноль. Работают обе схемы идентично, поэтому описание принципа действия здесь не требуется.

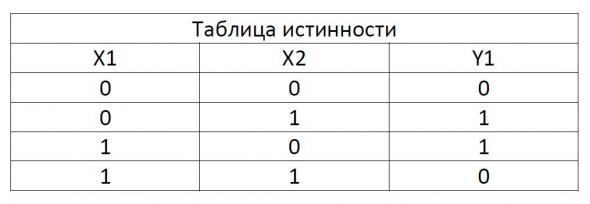

Работу выше описанных устройств иллюстрирует временная диаграмма:

Рисунок 3 – Временная диаграмма RS-триггера

По вышеприведенному описанию работы триггера составим таблицу истинности («*» - невозможное состояние):

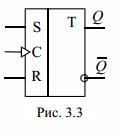

На схемах RS-триггер показывается как отдельное устройство, а не совокупность логических элементов, и имеет свое условное обозначение:

Рисунок 4 – Графическое обозначение асинхронного RS-триггера

22 Синхронные RS-триггеры. Схема, работа, таблица состояний, диаграммы работы.

В синхронных триггерах, кроме информационных импульсов, используют последовательности тактовых импульсов. Переход триггера в следующее состояние происходит только в момент прихода тактового импульса при наличии сигналов на информационных входах. Срабатывание синхронного триггера может происходить либо при воздействии фронта тактового импульса, либо его среза.

Рассмотрим работу тактируемого фронтом RS -триггера, условное графическое обозначение которого показано на рис. 3.3.

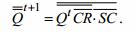

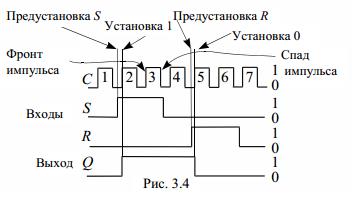

Наличие синхронизирующего входа C (clock) вносит изменения в работу триггера, временные диаграммы сигналов которого иллюстрирует рис. 3.4. Тактовый импульс C не оказывает никакого влияния на состояние выхода Q, когда на обоих входах установлен уровень логического 0. Во время прохождения импульса 1 триггер находится в режиме хранения. В момент предварительной установки входа S, когда на вход подается логическая 1, выход Q остается в прежнем состоянии Q = 0, и только на фронте тактового импульса 2 происходит его переключение к 1. Тактовые импульсы 3 и 4 не влияют на состояние выхода Q. Во время прохождения импульса 3 триггер находится в режиме установки 1, во время прохождения импульса 4 - в режиме хранения. Затем логическая 1 подается на вход R (предустановка входа R). На фронте импульса 5 происходит сброс (очистка) выхода Q путем установки его в состояние 0. Во время прохождения импульсов 5 и 6 триггер находится в режиме установки 0, во время прохождения импульса 7 - в режиме хранения. Подробное описание работы синхронного RS триггера позволяет составить его таблицу истинности и записать характеристическое уравнение:

23 D-триггер. Схема, работа, таблица состояний, диаграммы работы.

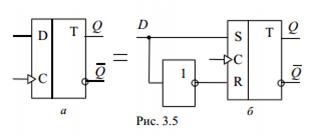

Условное графическое обозначение D -триггера приведено на рис. 3.5, а. D -триггер часто называют триггером с задержкой (delay).

Слово «задержка» здесь характеризует то, что происходит с данными (информацией), поступающими на вход D. Информационный сигнал (0 или 1), поступающий на этот вход, задерживается в триггере ровно на один такт, прежде чем появляется на выходе Q. Принцип работы D -триггера характеризует таблица истинности (табл. 3.2). Сигнал на выходе Q в такте t +1 (см. столбец Q t+1) повторяет сигнал, который был на входе D в предыдущем такте t.

Таблица 3.2

| D | Ct | Qt | Qt +1 | Режим работы |

| Уст«0» | |||

| Хранение | |||

| ||||

| Уст«1» |

D-триггер можно получить из тактируемого RS-триггера, добавляя к последнему инвертор, как показано на рис. 3.5, б. Подобная реализация возможна исходя из законов алгебры логики. Если в характеристическом уравнении RS -триггера заменить сигнал S на D, а сигнал R – на инверсию сигнала D, то получим логическое выражение D триггера:

,

,

реализацию которого можно провести, например, на логических элементах И-НЕ.

24 Счетчики. Классификация счетчиков

Счетчик - устройство, предназначенное для подсчета числа сигналов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах. Кроме того, счетчики могут выполнять и не столь очевидные функции: их, например, можно использовать для адресации, в качестве делителей частоты и элементов памяти. Количество разрядов счетчика определяется наибольшим числом, которое должно быть получено в каждом конкретном случае. В общем случае счетчик имеет M = 2N устойчивых состояний. Под действием входных сигналов счетчик, установленный в определенное состояние, сохраняет его до тех пор, пока на вход не поступит следующий сигнал. При подаче на вход счетчика M входных сигналов на выходе его возникает сигнал переполнения и счетчик возвращается в начальное состояние, т.е. счет единичных сигналов осуществляется в нем по модулю M.

По целевому назначению счетчики подразделяются на простые (суммирующие и вычитающие) и реверсивные. На простые счетчики сигналы поступают только с одним знаком, т.е. эти счетчики имеют переходы от состояния к состоянию только в одном направлении. Так, показание суммирующего счетчика при подаче на вход очередного единичного сигнала увеличивается на 1. Реверсивные счетчики предназначены для работы в режиме сложения и вычитания.

По способу организации цепей переноса между разрядами различают счетчики с последовательным (сквозным), групповым и частично групповым переносом.

По способу организации счета счетчики подразделяются на асинхронные и синхронные. В асинхронных счетчиках сигнал от разряда к разряду передается естественным путем в различные интервалы времени в зависимости от сочетаний входных сигналов. В синхронных счетчиках сигналы от разряда к разряду передаются принудительным путем с помощью тактовых сигналов.

Основными характеристиками счетчика являются:

- модуль счета - число устойчивых состояний счетчика, т.е. предельное число входных сигналов, которое может сосчитать счетчик;

- разрешающая способность - минимально допустимый период следования входных сигналов, обеспечивающий надежную работу счетчика;

- время регистрации - интервал времени между моментами поступления входного сигнала и окончания самого длинного переходного процесса в счетчике.

25 Суммирующий двоичный счетчик ИЕ5. Схема. Диаграммы напряжений.

Функциональные схемы счетчика типа ИЕ5 представлены на рис.178 - 180.

Счетчик построен следующим образом: в каждой ИС первый из триггеров имеет отдельный вход С1 и прямой выход три остальных триггера соединены между собой так что образуют делитель на 8 в ИС типа ИЕ5. При соединении выхода первого триггера со входом С2 цепочки из трех триггеров образуются четырехразрядные счетчики, позволяющие производить деление частоты входного сигнала С1 соответственно на 16

ИС имеют по два входа R0 установки в 0, объединенные по схеме " И". Сброс (установка в 0) триггеров производится при подаче уровней логической единицы на оба входа R0. При воздействии на оба эти входа логической 1 первый и четвертый триггеры переходят в единичное состояние, а остальные - в нулевое. Входы R0 и R9 изменяют состояние триггеров счетчика независимо от того, действует синхроимпульс или нет.

Наличие входов установки, объединенных по схеме " И", позволяет строить делители частоты с различными коэффициентами деления в пределах от 2 до 16 без использования дополнительных логических элементов.

Принцип построения делителя частоты на N следующий:

- число N представляется в двоичном коде (N = 9(10) = 1001(2));

- определяются номера триггеров, которые необходимо установить в единичное состояние (третий и нулевой);

- выходы третьего и нулевого триггеров соединяются со входами R0.

В этом случае до прихода девятого импульса счетчик работает в обычном режиме подсчета входных импульсов (состояние счетчика увеличивается на 1 с каждым входным импульсом). Девятый импульс переводит счетчик в состояние 9, при котором на выходах третьего и нулевого триггеров формируются уровни логической 1. Эти выходы соединены со входами К0, поэтому происходит обнуление всех триггеров счетчика. Поэтому при непрерывной подаче входных импульсов счетчик работает в сокращенном цикле от 0 до 8 (девятое состояние появляется кратковременно на время обнуления триггеров, для ИС 133-й серии t9=10 нс)

При разработке измерительной аппаратуры, а также во многих других случаях желательно обеспечивать отображение информации в десятичной системе счисления. При их отсутствии возможно реализовать декады на счетчике типа ИЕ5 (рис.181, 182).

Временные графики работы декады на основе ИС типа ИЕ5 представлены на рис.183.

В таблице 28 приведены номера выводов ИС типа ИЕ5, которые надо соединить между собой для получения различных коэффициентов пересчета K (при использовании ИС 134ИЕ5 необходимо заменить выводы 1, 3, 12, 8, 11 на соответственно 8, 1, 13, 10, 12). Все делители, полученные соединением выводов ИС по табл. 28, работают по одному принципу: при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка триггеров счетчика в нулевое состояние.

На рис.184 показана реализация делителя с коэффициентом деления 7. Таблица 27 поясняет принцип работы делителя на 7.

Таблица 28

ИС позволяет наращивать разрядность счетчика (рис. 185)

Максимальное время переключения 12-разрядного счетчика в три раза больше времени переключения 4 - разрядного.

26 Классификация и основные характеристики ЦАП.

Цифро-аналоговые преобразователи (ЦАП) — устройства, предназначенные для преобразования входного кода, сформированного совокупностью входных логических сигналов, в эквивалентное значение выходного напряжения, тока или сопротивления в соответствии с законом преобразования.

Существует несколько схем, каждая из которых служит базой для построения многих разновидностей ЦАП соответствующего класса (рис.1.1-1.3). Для формирования требуемых уровней аналоговые ключи, управляемые цифровыми сигналами aj, либо подключают к выходу ЦАП необходимое количество источников опорных сигналов bi (рис. 1.1, 1.2), либо устанавливают соответствующее дискретное значение коэффициента деления (рис. 1.3).

Работа таких ЦАП описывается уравнением

сj=mjb, j= 0, 1, 2…,

где сj - выходной аналоговый сигнал; mj - коэффициент передачи ЦАП по току или напряжению; b - опорный аналоговый сигнал; j - порядковый номер цифрового входного сигнала по мере возрастания его значений. Отсюда следует, что собственно преобразованию подвергается опорный аналоговый сигнал, а цифровой сигнал является модулирующим. При изменении значения aj на единицу младшего разряда (ЕМР) значение сj увеличивается или уменьшается на значение h, называемое шагом квантования.

По принципу формирования выходного сигнала ЦАП подразделяются на:

1. ЦАП с суммированием токов.

Рис. 1.1 ЦАП с суммированием токов

где сj —выходной аналоговый сигнал;

b —опорный аналоговый сигнал;

aj —управляющие цифровые сигналы.

2.ЦАП с суммированием напряжений

Рис. 7.2 ЦАП с суммированием напряжений

Существуют различные способы построения ЦАП с суммированием напряжений на основе схемы 1.2. Следует отметить, что у большинства из них выходное сопротивление изменяется в широких пределах, а ключи и источники опорных сигналов не связаны с нулевой шиной. В последнее время такие ЦАП появились в микроэлектронном исполнении(рис.1.2а). К последовательной резистивной схеме с общим сопротивлением 256Rприложен сигнал источника опорного напряжения (ИОН). В процессе преобразования общее сопротивление цепи не меняется, поэтому на каждом из резисторов создаётся стабильное падение напряжения. При помощи системы ключей в соответствии с кодом ajопределённая сумма этих напряжений поступает на выход.

a b

Рис.1.2 Схема 8-ми разрядного ЦАП с суммированием напряжений

Не смотря на некоторую громоздкость рассмотренной схемы, при современном уровне микроэлектронной технологии на её основе можно создавать недорогие преобразователи среднего качества. Достоинство таких схем состоит в гарантированной монотонности характеристики преобразования.

3.ЦАП с делением напряжений.

Рис. 3.3 ЦАП с делением напряжений

ЦАП с последовательными делителями напряжения содержат два последовательно соединённых управляемых резистора, образующих плечи делителя напряжения Rj и Rj'. Сопротивления этих резисторов определяются следующими соотношениями:

где aij=0 или 1, если i-ый ключ соответственно разомкнут или замкнут. Коэффициент передачи ЦАП равен

mj=Rj /(Rj+Rj').

Поскольку сопротивления управляются инверсным цифровым сигналом, сумма Rj+Rj' остаётся постоянной во всём диапазоне преобразования. Выходное сопротивление равно Rj. Следовательно, ЦАП с последовательными делителями напряжения характеризуются постоянным входным и изменяющимся выходным сопротивлениями.

По характеру опорного сигнала ЦАП подразделяются на:

1. ЦАП с фиксированным опорным сигналом;

2. ЦАП перемножающего типа (с изменяющимся опорным сигналом).

Основу ЦАП составляют наборы эталонных базисных элементов и совокупность электронных ключей, соединяющих базисные элементы в соответствии с заданным законом преобразования. Наиболее часто в качестве базисных элементов используются:

- источники двоично взвешенных токов;

- наборы двоично взвешенных резисторов;

- резистивные матрицы.

В качестве электронных ключей могут использоваться биполярные или КМОП транзисторы в ключевом режиме.

27 Параллельные ЦАП с суммированием весовых токов.

Большинство схем параллельных ЦАП основано на суммировании токов, сила каждого из которых пропорциональна весу цифрового двоичного разряда, причем должны суммироваться только токи разрядов, значения которых равны 1. Пусть, например, требуется преобразовать двоичный четырехразрядный код в аналоговый сигнал тока. У четвертого, старшего значащего разряда (СЗР) вес будет равен 23=8, у третьего разряда – 22=4, у второго – 21=2 и у младшего (МЗР) – 20=1. Если вес МЗР I МЗР=1 мА, то I СЗР=8 мА, а максимальный выходной ток преобразователя I вых.макс=15 мА и соответствует коду 11112. Понятно, что коду 10012, например, будет соответствовать I вых=9 мА и т.д. Следовательно, требуется построить схему, обеспечивающую генерацию и коммутацию по заданным законам точных весовых токов. Простейшая схема, реализующая указанный принцип, приведена на рис. 3.

Сопротивления резисторов выбирают так, чтобы при замкнутых ключах через них протекал ток, соответствующий весу разряда. Ключ должен быть замкнут тогда, когда соответствующий ему бит входного слова равен единице. Выходной ток определяется соотношением

При высокой разрядности ЦАП токозадающие резисторы должны быть согласованы с высокой точностью. Наиболее жесткие требования по точности предъявляются к резисторам старших разрядов, поскольку разброс токов в них не должен превышать тока младшего разряда. Поэтому разброс сопротивления в k-м разряде должен быть меньше, чем

∆ R/R=2–k

Из этого условия следует, что разброс сопротивления резистора, например, в четвертом разряде не должен превышать 3%, а в 10-м разряде – 0, 05% и т.д.

Рассмотренная схема при всей ее простоте обладает целым букетом недостатков. Во-первых, при различных входных кодах ток, потребляемый от источника опорного напряжения (ИОН), будет различным, а это повлияет на величину выходного напряжения ИОН. Во-вторых, значения сопротивлений весовых резисторов могут различаться в тысячи раз, а это делает весьма затруднительной реализацию этих резисторов в полупроводниковых ИМС. Кроме того, сопротивление резисторов старших разрядов в многоразрядных ЦАП может быть соизмеримым с сопротивлением замкнутого ключа, а это приведет к погрешности преобразования. В-третьих, в этой схеме к разомкнутым ключам прикладывается значительное напряжение, что усложняет их построение.

Эти недостатки устранены в схеме ЦАП AD7520 (отечественный аналог 572ПА1), разработанном фирмой Analog Devices в 1973 году, которая в настоящее время является по существу промышленным стандартом (по ней выполнены многие серийные модели ЦАП). Указанная схема представлена на рис. 4. В качестве ключей здесь используются МОП-транзисторы.

Рис. 4. Схема ЦАП с переключателями и матрицей постоянного импеданса

В этой схеме задание весовых коэффициентов ступеней преобразователя осуществляют посредством последовательного деления опорного напряжения с помощью резистивной матрицы постоянного импеданса. Основной элемент такой матрицы представляет собой делитель напряжения (рис. 5), который должен удовлетворять следующему условию: если он нагружен на сопротивление Rн, то его входное сопротивление Rвх также должно принимать значение Rн. Коэффициент ослабления цепи α =U2/U1 при этой нагрузке должен иметь заданное значение. При выполнении этих условий получаем следующие выражения для сопротивлений:

При двоичном кодировании α =0, 5. Если положить Rн=2R, то

Rs=R и Rp=2R

в соответствии с рис.4.

Поскольку в любом положении переключателей Sk они соединяют нижние выводы резисторов с общей шиной схемы, источник опорного напряжения нагружен на постоянное входное сопротивление Rвх=R. Это гарантирует неизменность опорного напряжения при любом входном коде ЦАП.

Согласно рис. 4, выходные токи схемы определяются соотношениями

а входной ток

Поскольку нижние выводы резисторов 2R матрицы при любом состоянии переключателей Sk соединены с общей шиной схемы через низкое сопротивление замкнутых ключей, напряжения на ключах всегда небольшие, в пределах нескольких милливольт. Это упрощает построение ключей и схем управления ими и позволяет использовать опорное напряжение из широкого диапазона, в том числе и различной полярности. Поскольку выходной ток ЦАП зависит от Uоп линейно (см. (8)), преобразователи такого типа можно использовать для умножения аналогового сигнала (подавая его на вход опорного напряжения) на цифровой код. Такие ЦАП называют перемножающими (MDAC).

Точность этой схемы снижает то обстоятельство, что для ЦАП, имеющих высокую разрядность, необходимо согласовывать сопротивления R0 ключей с разрядными токами. Особенно это важно для ключей старших разрядов. Например, в 10-разрядном ЦАП AD7520 ключевые МОП-транзисторы шести старших разрядов сделаны разными по площади и их сопротивление R0 нарастает согласно двоичному коду (20, 40, 80, …, 640 Ом). Таким способом уравниваются (до 10 мВ) падения напряжения на ключах первых шести разрядов, что обеспечивает монотонность и линейность переходной характеристики ЦАП. 12-разрядный ЦАП 572ПА2 имеет дифференциальную нелинейность до 0, 025% (1 МЗР).

ЦАП на МОП ключах имеют относительно низкое быстродействие из-за большой входной емкости МОП-ключей. Тот же 572ПА2 имеет время установления выходного тока при смене входного кода от 000...0 до 111...1, равное 15 мкс. 12-разрядный DAC7611 фирмы Burr-Braun имеет время установления выходного напряжения 10 мкс. В то же время ЦАП на МОП-ключах имеют минимальную мощность потребления. Тот же DAC7611 потребляет всего 2, 5 мВт. В последнее время появились модели ЦАП рассмотренного выше типа с более высоким быстродействием. Так 12-разрядный AD7943 имеет время установления тока 0, 6 мкс и потребляемую мощность всего 25 мкВт. Малое собственное потребление позволяет запитывать такие микромощные ЦАП прямо от источника опорного напряжения. При этом они могут даже не иметь вывода для подключения ИОН, например, AD5321.

28 АЦП с последовательным счетом. Схема. Диаграммы напряжения. Принцип действия.

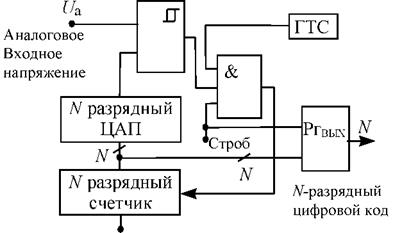

Во многих АЦП в цепи обратной связи используется ЦАП. Простейшим АЦП с ЦАП в цепи обратной связи является АЦП последовательного счета счетный АЦП (рис. 8.7).

рис. 8.7

Цифровой выход N-разрядного двоичного счетчика соединен с N-разрядным ЦАП, который вырабатывает выходное напряжение ступенчатой формы. Выходное напряжение ЦАП дискретно увеличивается от 1U0(МЗР) до напряжения полной разрядной сетки 2NU0(МЗР). На компараторе это напряжение сравнивается с входным аналоговым напряжением, и до тех пор, пока напряжение ЦАП ниже аналогового входного напряжения Ua, на выходе компаратора присутствует высокий уровень. Этот уровень удерживает вентиль (схема 3И) в открытом состоянии, и синхроимпульсы, проходя через него, попадают на счетчик, увеличение выходного, кода которого вызывает дальнейшее нарастание выходного напряжения ЦАП. Как только напряжение ЦАП становится выше уровня аналогового входного напряжения, на выходе компаратора появляется низкий уровень. При этом вентиль закрывается, и счетчик перестает считать. Через некоторое время уровень сигнала СТРОБ становится высоким, N -разрядный выходной регистр становится доступным для записи информации, и двоичный код со счетчика поступает на цифровой выход ЦАП. После окончания импульса СТРОБ импульс СБРОС производит обнуление счетчика, после чего он снова начинает считать, и таким образом начинается новый цикл преобразования.

Для обработки входного напряжения полной разрядной сетки в N -разрядном счетном преобразователе необходимо 2 N синхроимпульсов, поэтому такой тип АЦП относится к относительно медленным преобразователям. В 14-разрядном АЦП такого типа время преобразования равно 214ТC = 16384 ТС. Если принять ТС = 100 нс, то результирующее время преобразования будет 1, 64 мс, а соответствующая скорость - 610 циклов преобразования в секунду.

Точность счетного АЦП является функцией напряжения смещения, коэффициента усиления по напряжению компаратора и точности ЦАП. Чаще всего основным фактором, определяющим точность АЦП, является точность ЦАП.

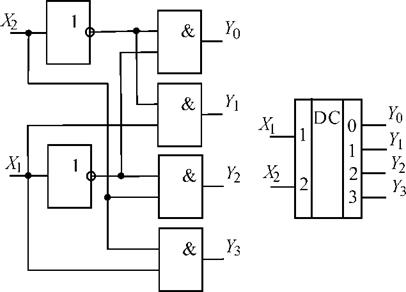

29 Дешифраторы. Схема. Диаграммы напряжения на примере дешифратора с двух входов на четыре выхода.

Дешифратором называется комбинационная схема, служащая для преобразования кодов. На рис. 2.1, а показана принципиальная схема дешифратора, имеющего два входа X1 и X2, реализующего четыре минтерма Y0, Y1, Y2, Y3 (дешифратор 2х4). Условное графическое обозначение данного дешифратора приведено на рис. 2.1, б. Схема выполняет операцию преобразования двоичного позиционного кода в унитарный цифровой, т.е. каждой комбинации входных сигналов, согласно правилам перевода двоичных чисел в десятичные, будет соответствовать сигнал высокого уровня (H) только на одном из выходов.

а б

Рис. 2.1

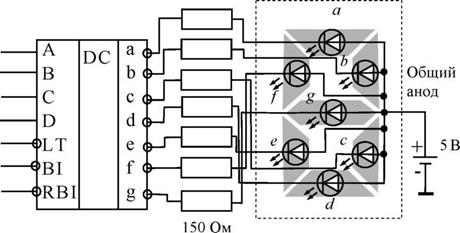

Одним из применений дешифратора является преобразование кода 8421 в код семисегментного индикатора. На индикаторе при этом появляется десятичное число. В схеме, представленной на рис. 2.2, используется ТТЛ ИС 7447А (аналог К155ИД2). Число, которое представлено в коде 8421 и подлежит декодированию, подается на входы, обозначенные буквами D, C, B и A. При возбуждении сигналом низкого уровня (L) вход контроля свечения (LT) активизирует все выходы. При подаче такого же возбуждающего сигнала на гасящий вход (BI) обеспечивается появление высоких уровней на всех выходах, что вызывает сброс прежних показаний индикатора. При возбуждении сигналом низкого уровня входа последовательного гашения (RBI) сброс индикатора осуществляется только в том случае, если на нем высвечены нули. Отметим, что запрещенными сигналами на входе дешифратора являются двоичные коды, эквивалентные десятичным числам 10  15 (на индикаторе будут отображены неполные цифровые изображения).

15 (на индикаторе будут отображены неполные цифровые изображения).

Рис. 2.2

Список использованных источников

1 Tитце У., Шенк К., Полупроводниковая схемотехника, пер. с нем., M., 1982. А. В. Степанов.

2 Основы вычислительной техники: Учебное пособие/ Д.П. Гонтов, К.Г. Кречетников и др: Владивосток: ТОВВМУ, 1996.

3 Каган Б.М. Электронные вычислительные машины и системы: Учебное пособие для вузов. – М.: Энергоатомиздат, 1991.

4 Калиш Г.Г. Основы вычислительной техники. Учеб. пособ. для средн. проф. учебных заведений. – М.: Высш. Шк., 2000.

5 Евреинов Э. В. Цифровая и вычислительная техника. – М.: Энергоатомиздат, 1991.

6 Цифровые устройства и микропроцессоры. Сборник заданий для лабораторных работ/ А. А. Гайзюмов, Д. П. Гонтов, А. Н. Карелин и др.: Владивосток: ТОВМИ, 1999.

7 Галиев А.Л., Галиева Р.Г, Элементы и устройства автоматизированных систем управления: Учеб. пособие. - Стерли- тамак: Стерлитамак. гос. пед. акад., 2008. - 220 с.

8 Чернышев А.Ю. Электронная и микропроцессорная техника: учебное пособие / А.Ю. Чернышев, Е.А. Шутов; Томский политехнический университет. - Томск: Изд-во Томского политехнического университета, 2013. - 118 с.

|

|